#### **Final Project**

# Analysis and design of resonant dc/dc converters for automotive applications

Institut für Elektrische Maschinen, Antriebe und Bahnen Prof. Dr.-Ing. M. Henke

Bearbeiter : David Jaunsaras Munarriz

Betreuer : Dipl.-Ing. Niklas Langmaack

Eingereicht am: 23. Juni 2014

## **Sworn declaration**

I herewith declare under oath that I have completed the present paper independently making use only of the specified literature and aids. Parts that have been taken literally or correspondingly from published or unpublished texts or sources have been labeled as such. This paper, in this form or in any other, has not been submitted to an examination board and has not been published.

Braunschweig, den 23. Juni 2014

# **List of Contents**

| 1 | INT | RODU                                                   | CTION                                       | 1  |

|---|-----|--------------------------------------------------------|---------------------------------------------|----|

| 2 | RES | SONAN                                                  | NT THEORY                                   | 2  |

|   | 2.1 | Resonant Switching theory and converter classification |                                             | 2  |

|   |     | 2.1.1                                                  | Zero Voltage Switching                      | 3  |

|   |     | 2.1.2                                                  | Zero Current Switching                      | 3  |

|   | 2.2 | Overv                                                  | view on resonant DC-DC converter topologies | 4  |

|   |     | 2.2.1                                                  | Series Resonant Converter (SRC)             | 4  |

|   |     | 2.2.2                                                  | Parallel Resonant Converter (PRC)           | 6  |

|   |     | 2.2.3                                                  | Series Parallel Resonant Converter (SPRC)   | 8  |

|   |     | 2.2.4                                                  | LLC Converter                               | 9  |

|   |     | 2.2.5                                                  | CLLC Converter                              | 12 |

|   | 2.3 | LLC 1                                                  | RESONANT HALF – BRIDGE CONVERTER            | 14 |

|   |     | 2.3.1                                                  | Configuration                               | 14 |

|   |     | 2.3.2                                                  | Modeling                                    | 15 |

|   |     | 2.3.3                                                  | Design considerations                       | 16 |

|   |     | 2.3.4                                                  | Selecting design parameters                 | 17 |

|   | 2.4 | LLC 1                                                  | RESONANT FULL – BRIDGE CONVERTER            | 20 |

|   |     | 2.4.1                                                  | Configuration                               | 20 |

|   |     | 2.4.2                                                  | Modeling                                    | 21 |

|   |     | 2.4.3                                                  | Design considerations                       | 21 |

|   |     | 2.4.4                                                  | Selecting design parameters                 | 21 |

|   | 2.5 | CLLC                                                   | C BIDIRECTIONAL RESONANT CONVERTER          | 22 |

|   |     | 2.5.1                                                  | Configuration                               | 22 |

|   |     | 2.5.2                                                  | Modeling                                    | 23 |

|   |     | 2.5.3                                                  | Design considerations                       | 24 |

|   |     | 2.5.4                                                  | Selecting design parameters                 | 24 |

| 3        | DES                                                                        | SIGN A | ND SIMULATION                                        | 26 |

|----------|----------------------------------------------------------------------------|--------|------------------------------------------------------|----|

|          | 3.1                                                                        | DESI   | GNED EV AUXILIARY POWER SUPPLY                       | 26 |

|          |                                                                            | 3.1.1  | Design steps                                         | 26 |

|          |                                                                            | 3.1.2  | Simulation analysis and evaluation                   | 30 |

|          |                                                                            | 3.1.3  | Converter response against 10% load                  | 35 |

|          | 3.2<br>RES                                                                 |        | VANIC INSULATION FOR STANDARD EV ONBOARD T CONVERTER |    |

|          |                                                                            | 3.2.1  | Model 1                                              | 38 |

|          |                                                                            | 3.2.2  | Model 2                                              | 47 |

|          | 3.3                                                                        | EV A   | UXILIARY POWER SUPPLY FOR MILD HEV                   | 63 |

|          |                                                                            | 3.3.1  | Design steps                                         | 63 |

|          |                                                                            | 3.3.2  | Simulation analysis and evaluation                   | 65 |

|          | 3.4 GALVANIC INSULATION FOR EV FAST CHARGER WITH "VEHICLE TO GRID" FEATURE |        |                                                      |    |

|          |                                                                            | 3.4.1  | Design steps                                         | 69 |

|          |                                                                            | 3.4.2  | Simulation analysis and evaluation                   | 71 |

| 4<br>HAF | RDW                                                                        | ARE D  | C INSULATION FOR STANDARD EV ONBOARD ( ESIGN         | 75 |

|          | 4.1                                                                        |        | luction                                              |    |

|          | 4.2                                                                        | _      | Power side                                           |    |

|          |                                                                            | 4.2.1  | 1 · · · · 1 · · · · · · · · · · · · · ·              |    |

|          |                                                                            | 4.2.2  | Transformer                                          |    |

|          |                                                                            | 4.2.3  | 1 1                                                  |    |

|          | 4.3                                                                        |        | ol side                                              |    |

|          |                                                                            |        | MOSFETs Drivers                                      |    |

|          |                                                                            | 4.3.2  | Microcontroller                                      |    |

|          |                                                                            | 4.3.3  | Voltage measurement                                  |    |

|          |                                                                            | 4.3.4  | Temperature measurement                              |    |

|          |                                                                            |        | Control Voltage                                      |    |

|          | 4.4                                                                        | Circui | it design                                            | 87 |

| 5        | Con                                                                        | clusio | ons                                                  | 90 |

|          |                                                                            |        |                                                      |    |

| Α | Ann | nex                                                          | I    |

|---|-----|--------------------------------------------------------------|------|

|   | A.1 | LLC RESONANT CONVERTER DESIGNING GUIDE                       |      |

|   |     | A.1.1 Define working conditions                              | II   |

|   |     | A.1.2 Transformer turn ratio, n                              | II   |

|   |     | A.1.3 Gain, Mg                                               | II   |

|   |     | A.1.4 Inductance ratio, Ln* and Quality factor, Qe           | II   |

|   |     | A.1.5 Quality factor, Qe                                     | IV   |

|   |     | A.1.6 Obtain fn and check ZVS condition                      | VI   |

|   |     | A.1.7 Load resistant (Rl) and equivalent load resistant (Re) | VII  |

|   |     | A.1.8 Resonant parameters                                    | VII  |

|   |     | A.1.9 Resonant frequencies, f1, f0                           | VII  |

|   |     | A.1.10 Verify resonant-circuit converter                     | VII  |

|   |     | A.1.11 Dead time, Tdead                                      | VIII |

|   | A.2 | CLLC RESONANT CONVERTER DESIGNING GUIDE                      | IX   |

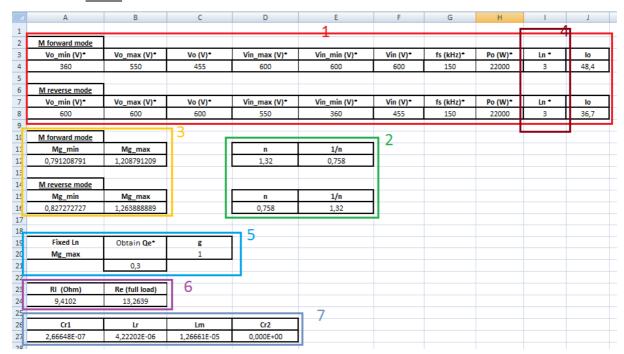

|   |     | A.2.1 Define working conditions for both modes               | IX   |

|   |     | A.2.2 Transformer turn ratio, n                              | X    |

|   |     | A.2.3 Gain, Mg                                               | X    |

|   |     | A.2.4 Inductance ratio, Ln*                                  | X    |

|   |     | A.2.5 Quality factor, Qe and g                               | XII  |

|   |     | A.2.6 Load resistant (Rl) and equivalent load resistant (Re) | XIII |

|   |     | A.2.7 Resonant parameters                                    | XIV  |

|   | A.3 | INDUCTANCE ANALYSIS FOR TRANSFORMERS                         |      |

|   |     | A.3.1 Theoretical summary                                    | XV   |

|   |     | A.3.2 Winding model                                          |      |

|   |     | A 3.3 Analysis                                               | XVII |

# **List of Tables**

| Table 1 Inductance values for model 1 | XVII    |

|---------------------------------------|---------|

| Table 2 Inductance values for model 2 | XVIII   |

|                                       |         |

| Table 3 Inductance values for model 3 | X V III |

# **List of Figures**

| Figure 2.1 Comparative soft and hard switching                     | 3  |

|--------------------------------------------------------------------|----|

| Figure 2.2 Resonant converter block diagram                        | 4  |

| Figure 2.3 Series resonant converter block diagram                 | 5  |

| Figure 2.4 Gain characteristic of SRC                              | 5  |

| Figure 2.5 Parallel resonant converter block diagram               | 7  |

| Figure 2.6 Gain characteristic of PRC                              | 7  |

| Figure 2.7 Series parallel resonant converter block diagram        | 8  |

| Figure 2.8 Gain characteristic of SPRC                             | 9  |

| Figure 2.9 LLC resonant converter block diagram                    | 10 |

| Figure 2.10 Gain characteristic of LLC                             | 10 |

| Figure 2.11 CLLC resonant converter block diagram                  | 12 |

| Figure 2.12 Gain characteristic of CLLC                            | 13 |

| Figure 2.13 Half-Bridge LLC Resonant Converter                     | 14 |

| Figure 2.14 Plot of voltage-gain function (Mg) with Ln = 5         | 16 |

| Figure 2.15 Peak-gain curve                                        | 18 |

| Figure 2.16 Full-Bridge LLC Resonant Converter                     | 20 |

| Figure 2.17 Full-Bridge CLLC Resonant Converter                    | 22 |

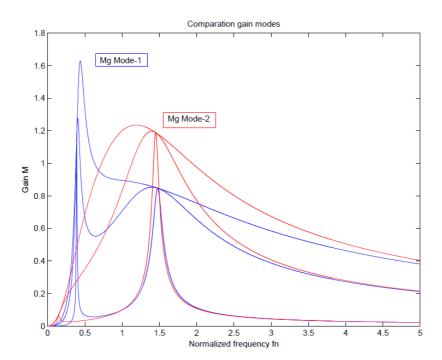

| Figure 2.18 Comparative gain between Mode-1 and Mode-2             | 24 |

| Figure 3.1 Peak-gain curve for Ln = 2                              | 28 |

| Figure 3.2 No load condition for Ln = 2                            | 28 |

| Figure 3.3 Verification of resonant-circuit design conditions      | 30 |

| Figure 3.4 Simulated Half-Bridge LLC Resonant Converter            | 31 |

| Figure 3.5 MOSFET voltage, diode current ands MOSFET current of S1 | 32 |

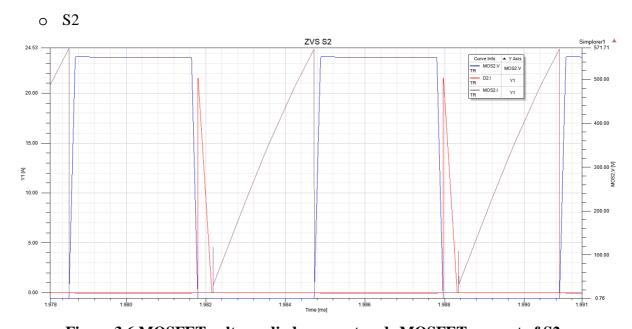

| Figure 3.6 MOSFET voltage, diode current ands MOSFET current of S2          | 32 |

|-----------------------------------------------------------------------------|----|

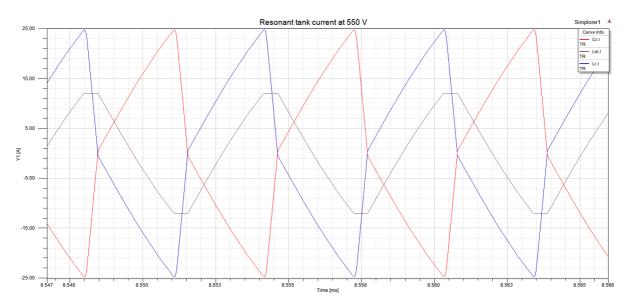

| Figure 3.7 Resonant tank current at 550 V                                   | 33 |

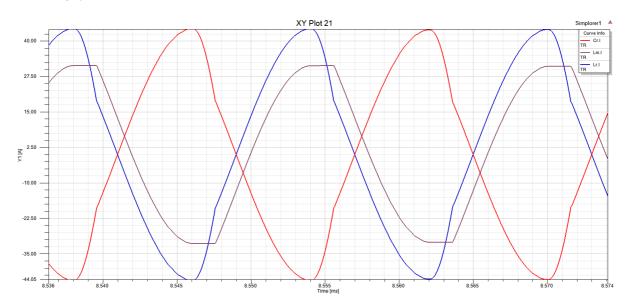

| Figure 3.8 Resonant tank current at 240 V                                   | 33 |

| Figure 3.9 Output-power response against input-voltage variation            | 34 |

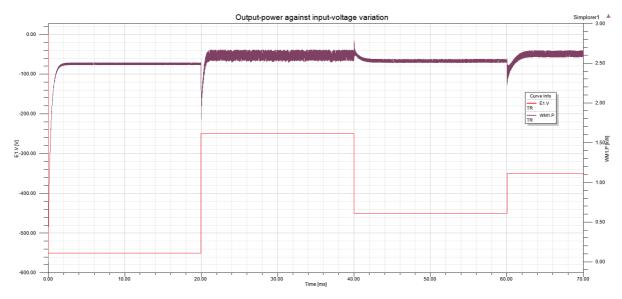

| Figure 3.10 Output-power response against input-voltage variation           | 34 |

| Figure 3.11 Converter response under 10% load condition                     | 35 |

| Figure 3.12 Verification of resonant-circuit design conditions              | 36 |

| Figure 3.13 Converter response under 10% load condition (with zoom)         | 37 |

| Figure 3.14 Peak-gain curve for Ln = 5                                      | 39 |

| Figure 3.15 Verification of resonant-circuit design conditions              | 41 |

| Figure 3.16 Simulated Half-Bridge LLC Resonant Converter                    | 42 |

| Figure 3.17 MOSFET voltage, diode current ands MOSFET current of S1 at 400V | 42 |

| Figure 3.18 MOSFET voltage, diode current ands MOSFET current of S2 at 400V | 43 |

| Figure 3.19 MOSFET voltage, diode current ands MOSFET current of S1 at 240V | 43 |

| Figure 3.20 MOSFET voltage, diode current ands MOSFET current of S2 at 240V | 44 |

| Figure 3.21 Resonant tank current at 400 V                                  | 45 |

| Figure 3.22 Resonant tank current at 240 V                                  | 45 |

| Figure 3.23 Output-power response against output-voltage variation          | 46 |

| Figure 3.24 Peak-gain curve for Ln = 2.5                                    | 48 |

| Figure 3.25 No load condition for Ln = 2.5                                  | 49 |

| Figure 3.26 Verification of resonant-circuit design conditions              | 50 |

| Figure 3.27 Simulated Half-Bridge LLC Resonant Converter                    | 51 |

| Figure 3.28 MOSFET voltage, diode current ands MOSFET current of S1 at 520V | 52 |

| Figure 3.29 MOSFET voltage, diode current ands MOSFET current of S2 at 550V | 52 |

| Figure 3.30 MOSFET voltage, diode current ands MOSFET current of S1 at 360V | 53 |

| Figure 3.31 MOSFET voltage, diode current ands MOSFET current of S2 at 360V | 53 |

| Figure 3.32 Output-power response against input/output-voltage variation    | 54 |

| Figure 3.33 Output-power against frequency variation at Vo = 360 V          | 55 |

| Figure 3.34 Output-power against frequency variation at Vo = 520 V          | 55 |

| Figure 3.35 Verification of resonant-circuit design conditions              | 58 |

| Figure 3.36 Simulated Full-Bridge LLC Resonant Converter                             | 59 |

|--------------------------------------------------------------------------------------|----|

| Figure 3.37 MOSFET voltage, diode current ands MOSFET current of S1 at 520V          | 59 |

| Figure 3.38 MOSFET voltage, diode current ands MOSFET current of S2 at 520V          | 60 |

| Figure 3.39MOSFET voltage, diode current ands MOSFET current of S1 at 360V           | 60 |

| Figure 3.40 MOSFET voltage, diode current ands MOSFET current of S2 at 360V          | 61 |

| Figure 3.41 Output-power response against output-voltage variation                   | 61 |

| Figure 3.42 Output-power against frequency variation at Vo = 360 V                   | 62 |

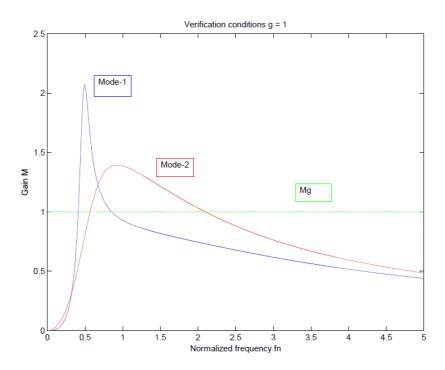

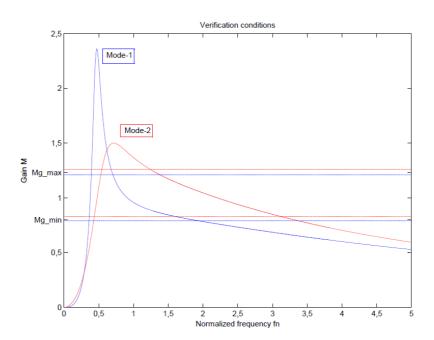

| Figure 3.43 Verification conditions g = 1                                            | 65 |

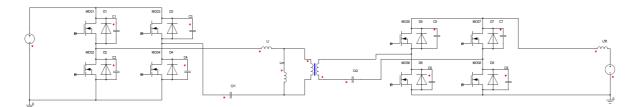

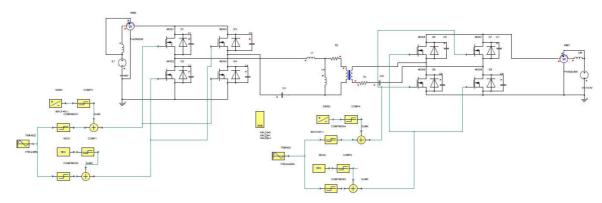

| Figure 3.44 Simulated Full-Bridge CLLC Resonant Converter                            | 66 |

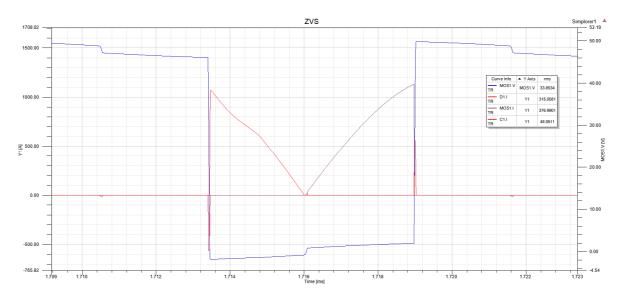

| Figure 3.45 ZVS condition for forward mode                                           | 66 |

| Figure 3.46 ZVS condition for reverse mode                                           | 67 |

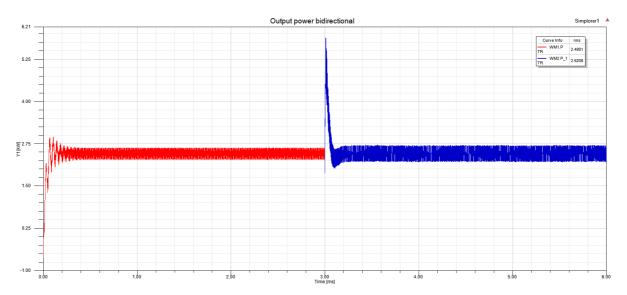

| Figure 3.47 Output power for bidirectional response                                  | 68 |

| Figure 3.48 Verification conditions $g = 1$                                          | 71 |

| Figure 3.49 Simulated Full-Bridge CLLC Resonant Converter                            | 72 |

| Figure 3.50 ZVS condition for forward mode at 360 V                                  | 72 |

| Figure 3.51 ZVS condition for reverse mode at 550 V                                  | 73 |

| Figure 3.52 Output power against output voltage variation reverse mode               | 73 |

| Figure 3.53 Output power against output voltage variation forward mode               | 74 |

| Figure 4.1 High level LLC converter block diagram                                    | 76 |

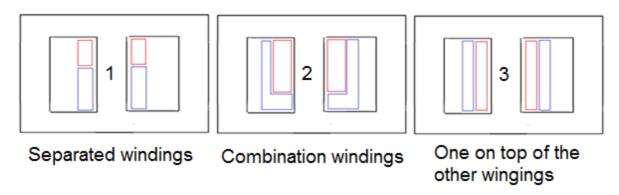

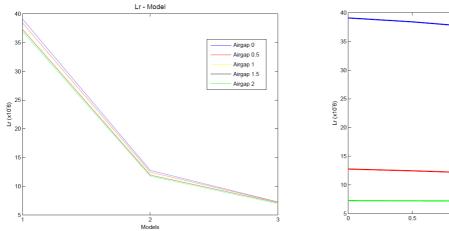

| Figure 4.2 Winding models                                                            | 79 |

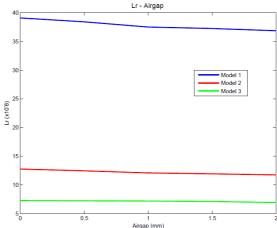

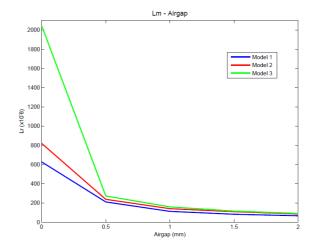

| Figure 4.3 Lr value against different winding models topology for different air gaps | 79 |

| Figure 4.4 Lr value against air gap variation                                        | 79 |

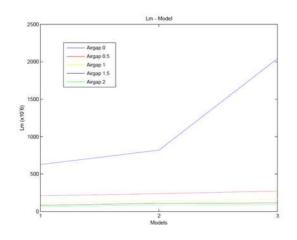

| Figure 4.5 Lm value against different winding models topology for different air gaps | 80 |

| Figure 4.6 Lm value against air gap variation                                        | 80 |

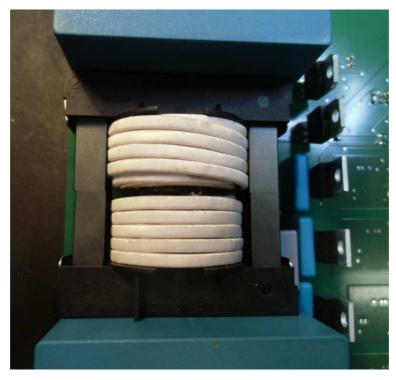

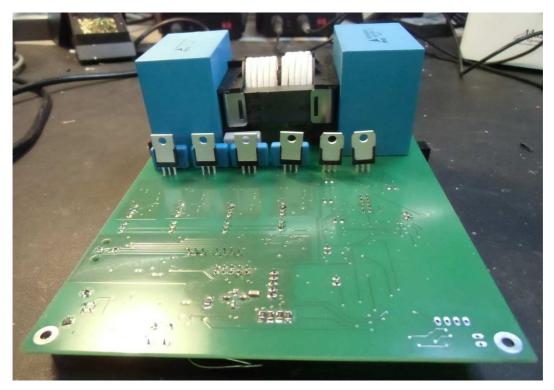

| Figure 4.7 Transformer for galvanic insulation for standard EV Onboard charger       | 81 |

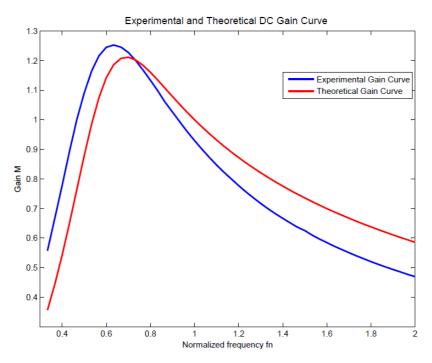

| Figure 4.8 Comparative of experimental and theoretical gain curve of the transformer | 82 |

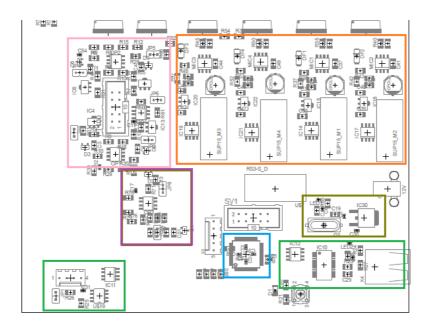

| Figure 4.9 Control Side of the printed board                                         | 83 |

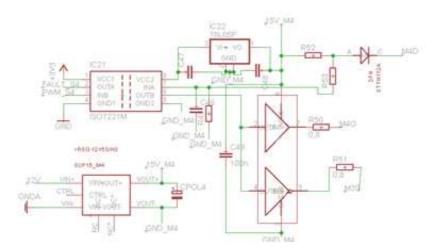

| Figure 4.10 MOSFET driver schematic circuit                                          | 84 |

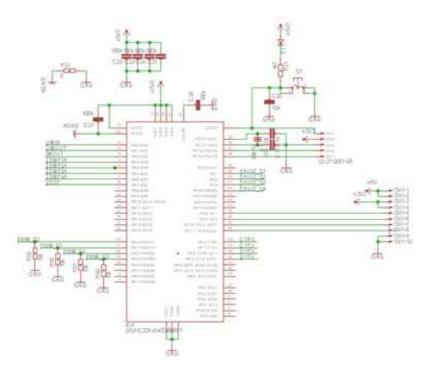

| Figure 4.11 Microcontroller schematic circuit                                        | 85 |

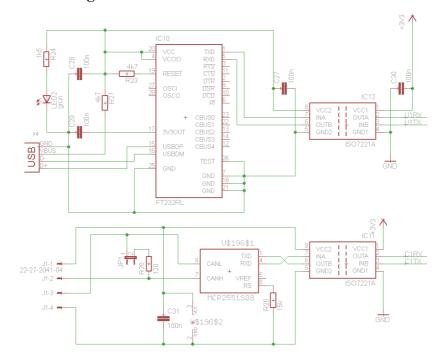

| Figure 4.12 USB communication and CAN bus circuit                                    | 85 |

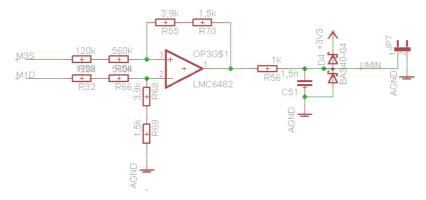

| Figure 4.13 Voltage measurement schematic circuit                                       | 86          |

|-----------------------------------------------------------------------------------------|-------------|

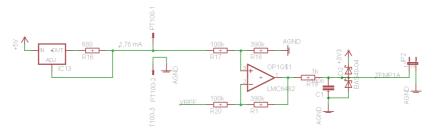

| Figure 4.14 Temperature measurement schematic circuit                                   | 86          |

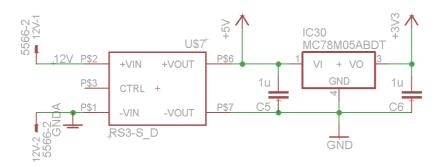

| Figure 4.15 Control voltage schematic circuit                                           | 87          |

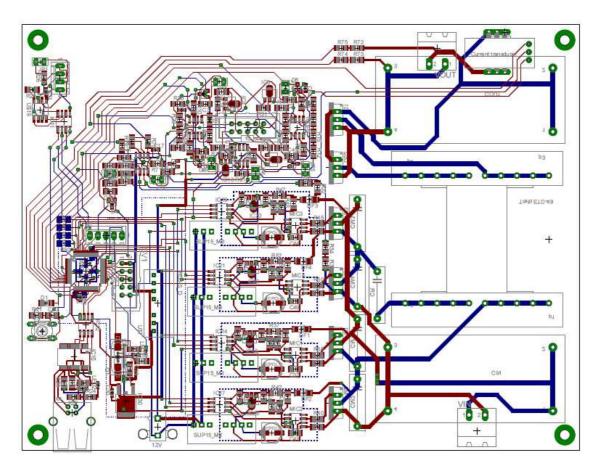

| Figure 4.16 Printed board for LLC converter                                             | 88          |

| Figure 4.17 Top layer of Galvanic insulation for a standard EV Onboard charger          | 88          |

| Figure 4.18 Bottom layer of Galvanic insulation for a standard EV Onboard charger       | · 89        |

| Figure A.1. 1 Helping Excel image                                                       | I           |

| Figure A.1. 2 Initial Ln = 2 value with Qe = 0                                          | III         |

| Figure A.1. 3 Matlab code                                                               | III         |

| Figure A.1. 4 Mg_ap image for different Ln                                              | IV          |

| Figure A.1. 5 Matlab Code                                                               | IV          |

| Figure A.1. 6 Matlab Mg_ap table                                                        | V           |

| Figure A.1. 7 Matlab Qe table                                                           | V           |

| Figure A.1. 8 Matlab Code                                                               | VI          |

| Figure A.1. 9 Matlab Graph                                                              | VI          |

| Figure A.1. 10 Matlab Code                                                              | VII         |

| Figure A.2 1 Helping Excel image                                                        | IX          |

| Figure A.2 2 Initial Ln = 2.5 value with Qe = 0                                         | XI          |

| Figure A.2 3 Matlab code                                                                | XI          |

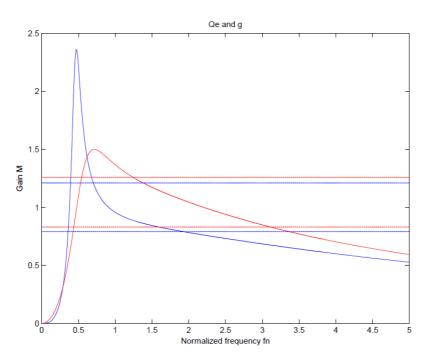

| Figure A.2 4 Curves for Qe and g                                                        | XII         |

| Figure A.2 5 Matlab Code                                                                | XIII        |

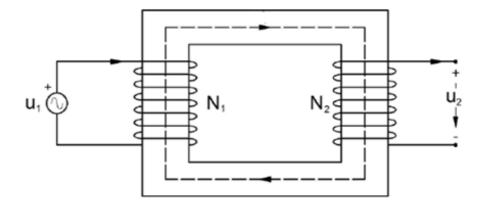

| Figure A.3 1 Electrical transformer                                                     | XV          |

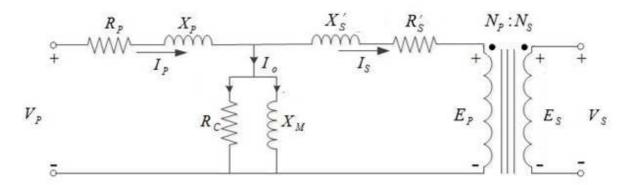

| Figure A.3 2 Exact equivalent transfomer circuit                                        | XVI         |

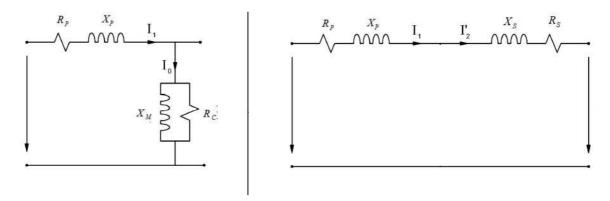

| Figure A.3 3 a) Open circuit test equivalent circuit. 3b) Short circuit test equivalent | ent circuit |

|                                                                                         | XVI         |

# **Acronyms**

AC Alternating Current

DC Direct Current

EMI Electromagnetic Interference

EV Electric Vehicle

FM Frequency Modulation

HEV Hybrid Electric Vehicle

PRC Parallel Resonant Converter

PWM Pulse-Width Modulation

SPRC Series-Parallel Resonant Converter

SR Synchronous Rectification

SRC Series Resonant Converter

ZCS Zero Voltage Switching

ZVS Zero Current Switching

### **Abstract**

With automobiles getting more electrified, DC-DC resonant converters are developed with renewed interest. Since, it is desirable to reduce the size of power supplies and the higher switching losses through zero-voltage switching (ZVS) feature. This thesis provides detailed information on designing LLC and bidirectional CLLC resonant converter topologies as well as the simulation of four typical converters in automotive applications. Furthermore, the hardware design and manufacture of an EV auxiliary power supply prototype is implemented.

#### **Keywords related to this work:**

- DC-DC resonant converter design

- LLC

- Bidirectional CLLC

- Zero-voltage switching (ZVS)

# Kurzfassung

Aufgrund zunehmender Elektrizierung von Automobilantrieben werden DC-DC Resonanzwandler mit neuem Interesse entwickelt. Entscheidend für den Einsatz im Automobilbereich sind geringe Abmessungen. Daher ist es wünschenswert die Größe der Stromversorgung und die höheren Schaltverluste durch Nullspannungsschaltung (ZVS) zu reduzieren. Dieses Masterarbeir bietet sowohl ausführliche Informationen zur LLC-Gestaltung und Auslegung der bidirektionalen CLLC-Resonanzwandler als auch die Simulation von vier typischen Wandlern in der Automobilanwendung. Ferner ist die Konstruktion der Hardware und Herstellung eines Prototypen der EV Hilfstromversorgung umzusetzen.

#### Stichwörter zu dieser Arbeit:

- DC-DC Resonanzwandler

- LLC

- Bidirektionaler CLLC

- Nullspannungsschaltung (ZVS)

1 INTRODUCTION 1

### 1 INTRODUCTION

The increasing demand for electric power in automobiles requires larger number of applications where DC-DC converters are used. To reduce the size of power supplies intended to use in modern electric power systems, it is desirable to raise the operating frequency to reduce the size of components. To decrease the higher switching losses resulting from higher frequency operation, resonant power conversion is receiving renewed interest.

Resonant converters, which were very investigated some decades ago, may achieve low switching loss and operate at high switching frequency. In resonant topologies, Series Resonant Converter (SRC), Parallel Resonant Converter (PRC), Series Parallel Resonant Converter (SPRC), LLC and CLLC are the most common topologies.

This thesis presents a design procedure for LLC and CLLC resonant converters, beginning with an overview on common topologies and operation behavior. To demonstrate how a design is created, four step-by-step automotive applications are presented. The thesis concludes with the hardware design and manufacture of one proposed application.

## **2 RESONANT THEORY**

This chapter introduces the resonant theory of DC-DC converters as well as an overview on common topologies. Moreover, a description of the process to obtain a suitable set of parameters for a specific design is proposed.

# 2.1 Resonant Switching theory and converter classification

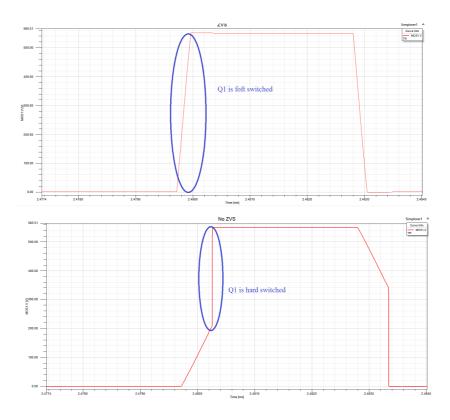

A way to reduce or eliminate some of the switching loss mechanisms (Figure 2.1 shows soft and hard switching of a MOSFET) is achieved when turn-on and turn-off transitions of semiconductors devices occur at zero voltage or current waveforms.

Figure 2.1 Comparative soft and hard switching

#### 2.1.1 Zero Voltage Switching

The ZVS turn-on is achieved by discharging the output capacitance of the switches before turning them on. Transistor turn-on transition occurs at zero voltage. ZVS brings some benefits such as low switching losses, reduction of the energy needed to drive switches, low noise and EMI generation.

The ZVS approach is preferred for the majority of carrier semiconductor devices such as MOSFETs.

#### 2.1.2 Zero Current Switching

The ZCS turn-off transition occurs at zero current. The ZCS approach is suitable for the minority of carrier semiconductor devices such as insulated-gate bipolar transistors and

power diodes

# 2.2 Overview on resonant DC-DC converter topologies

A general description of each circuit, advantages and disadvantages are presented here.

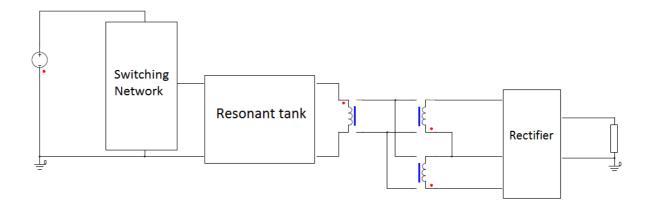

The difference between each topology is found in the resonant tank. Figure 2.2 shows a switching network, rectifier block and resonant tank.

Figure 2.2 Resonant converter block diagram

#### 2.2.1 Series Resonant Converter (SRC)

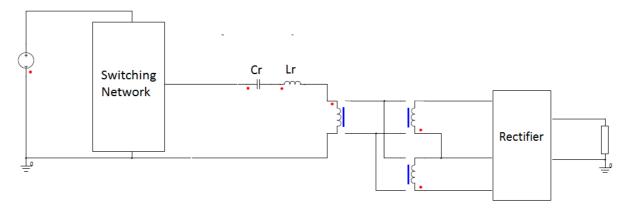

In series resonant converter, the tank is formed by resonant inductor (Lr) and resonant capacitor (Cr) and they constitute a series resonant tank as seen in Figure 2.3.

Figure 2.3 Series resonant converter block diagram

They are also in series with the load and it works as a voltage divider. The gain is always lower than the unity thus it works as a voltage divider. The maximum gain is obtained at resonant frequency since the impedance of series resonant tank will be lower at this frequency.

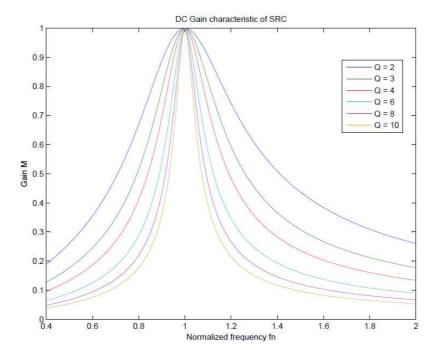

Figure 2.4 Gain characteristic of SRC

Two zones are differentiated in Figure 2.4 by the vertical of the resonant frequency. When the switching frequency is higher than resonant frequency, the converter will work under

ZVS condition. This region is chosen for the operating region because of ZVS. For lower frequency the converter will work under ZCS as explained in (1).

Main advantages and disadvantages of series resonant converter are presented here:

- No regulated output-voltage for no load case is the principle disadvantage in series resonant converter. Only applications with no load regulation required are available for this converter, since, as seen in Figure 2.4, low Q curves would be more horizontal.

- For applications with low output-voltage and high current is a disadvantage to have an output DC filter flowing high ripple current. High output-voltage and low output-current applications are more appropriate for these converters than low output-voltage and high output-current converters which are not perceived as suitable.

- ✓ Series resonant converter is suitable for full-bridge high power applications because of series resonant capacitors on the primary side act as a DC blocking capacitor.

- ✓ High load efficiency is preserved because of the current in the power devices decrease as the load decreases. It lets the power device conduction losses to be reduces as the load decreases.

#### 2.2.2 Parallel Resonant Converter (PRC)

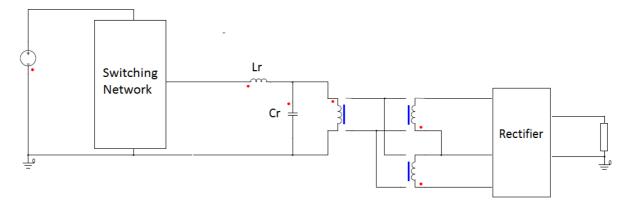

In this case this converter is called parallel resonant converter thus the load is in parallel with the resonant capacitor as seen in Figure 2.5. However, the resonant tank is still in series.

Figure 2.5 Parallel resonant converter block diagram

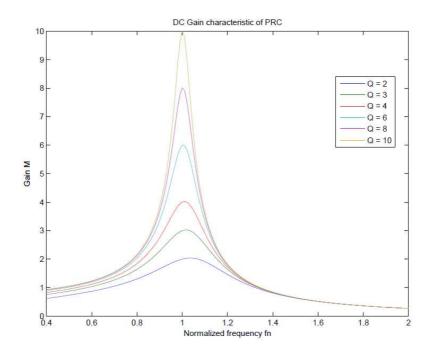

Figure 2.6 Gain characteristic of PRC

As seen in (1), ZVS is achieved on the right zone and for this converter the operation zone is also designed to obtain ZVS. To maintain the output-voltage regulated, high frequency variation is not needed. PRC has no regulation problem with light load and the operation region is smaller.

With higher frequency than resonant frequency the converter can control the output-voltage at no load condition (Q=0) how shows Figure 2.6.

Main advantages and disadvantages of parallel resonant converter are presented here:

- The conduction losses are almost constant in the converter, since the current into the resonant tank keeps constant when the frequency varies to regulate the output-voltage.

- ✓ Applications which have a narrow input voltage range and a relatively constant load to maintain the working point near the maximum design power are more appropriate.

- ✓ The parallel-resonant converter is suitable for low-output-voltage and high-outputcurrent applications. The current is limited by the resonant inductor making the PRC desirable for applications with high short-circuit requirements.

- ✓ Output-voltage is controlled with higher frequency than resonant frequency at no load condition.

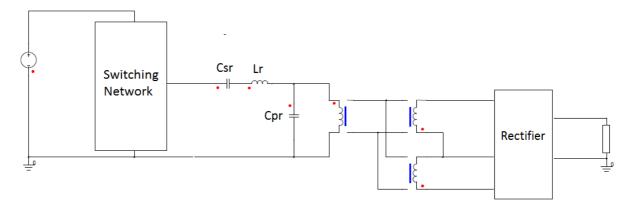

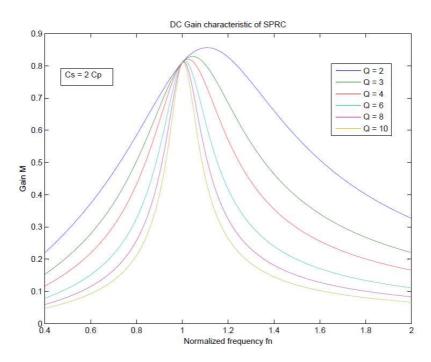

#### 2.2.3 Series Parallel Resonant Converter (SPRC)

The combination of series-converter and parallel-resonant results in a converter with better characteristics than both and removes their disadvantages. A wider frequency range and optimal selection of the resonant components are required.

Figure 2.7 Series parallel resonant converter block diagram

Figure 2.8 Gain characteristic of SPRC

ZVS is achieved designing the operation region on the right hand side. Highest resonant frequency makes normally the converter more efficient.

Main advantages and disadvantages of parallel resonant converter are presented here:

- $\checkmark$  No load regulation is achieved for SPRC when  $C_{pr}$  is not too small. Main disadvantage of SRC is removed.

- ✓ Constant circulating current independent of the load is avoided.

- Switching losses will increase at high input voltage when the input range is wide. Switching loss is still, a big penalty, similar to PWM converter at high input voltage.

A more detailed explication about these converters is found in (1).

#### 2.2.4 LLC Converter

The characteristics and operation of this converter are different; despite of LLC has the same

form as SPRC apart of magnetizing inductance as seen in Figure 2.9. Three resonant components form the LLC converter ( $L_r$ ,  $C_r$  and  $L_m$ ) and two resonant frequencies are induced. Low frequency is induced by  $C_r$  and  $L_m + L_r$  and the high frequency by  $C_r$  and  $L_r$ .

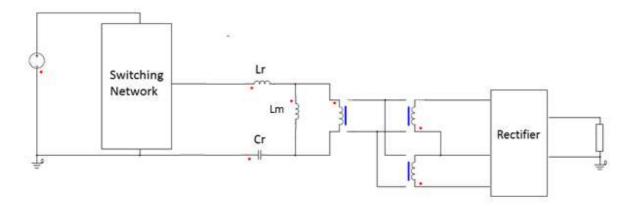

Figure 2.9 LLC resonant converter block diagram

Figure 2.10 Gain characteristic of LLC

In Figure 2.10 is possible to see how when the load becomes lighter the peak moves closer to  $f_1$ . On the other hand, the peak moves to f0 when the load becomes heavier. Comparing the converter behavior, it works more as PRC when the load is light and more as SRC when

the load is heavy. The gain characteristics can be either boost type or buck type, which means buck-boost converter.

As seen previously, Figure 2.10 is divided in three regions:

- Region 1: Switching frequency is higher than  $f_{r1}$ . ZVS is achieved in this region and it is also SRC operation region.

- Region 2: Between  $f_{r1}$  and  $f_{r2}$  is a multi resonant converter region. Depending on the load the converter will be under ZCS and ZVS condition.

- Region 3: Only ZCS is achieved in this overloaded region.

In general, LLC resonant converter is designed to operate in Region 1 and 2 because of output regulation and ZVS operation. To ensure ZVS operation, the operating range of this converter is above the  $f_{\rm r2}$  and the  $L_{\rm r}$  and  $C_{\rm r}$  are chosen to ensure at heavy load. The choice of the  $L_{\rm m}$  determines the switching frequency range and MOSFET turn-off current. With smaller  $L_{\rm m}$  more narrow operating range is set. However, MOSFET turn-off current will be higher which increases switching losses.

The most efficiency working point is to allow LLC converter to work at the resonant frequency  $f_{r1}$ , thus switching losses and circulating energy are reduced working under these conditions. To maintain the output voltage regulated when the load and the input voltage vary, the operation frequency is modified. The ZVS operation of the MOSFETs is very important for the efficiency of the LLC resonant converter. A more detailed analysis about operating modes in LLC converter is presented in (2).

Main advantages and disadvantages of LLC resonant converter are presented here.

- ✓ Output regulation is controlled whit variations of switching frequency.

- ✓ ZVS capability for whole load range produces lower switching losses.

- ✓ The magnetic components can be integrated into magnetic core. The leakage inductance of a transformer can participate in resonant operation.

- **X** Conventional LLC converter is unidirectional.

Several variants are proposed to improve the converter possibilities (three level ZVS PWM

converter, secondary-side control); however, full-bridge topology is the most common. Lower current values are obtained with this topology in high voltage applications. It is also proposed full-bridge topology in the secondary side trying to reduce power losses through Synchronous Rectification (SR).

#### 2.2.5 CLLC Converter

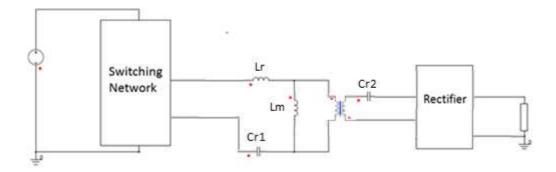

Apart for the extra resonant capacitor, the converter configuration is very similar to LLC converter. It has also ZVS but an additional property is obtained, bidirectionality.

Figure 2.11 CLLC resonant converter block diagram

In (3) a detailed analysis of different combinations of MOSFETs and IGBTs is carried out. For this converter ZVS + ZCS is preferred (ZVS primary side devices and ZCS secondary side devices) regardless of the direction of the power flow. The primary side changes depending on the power flow direction and the benefits of MOSFETs (associated with ZVS) in the primary side make that the MOSFETs are chosen in both sides. Since, with this topology the switching losses can be minimized.

Figure 2.12 Gain characteristic of CLLC

Theoretically, ZVS + ZCS can be obtained through PWM and FM. However, this topology is not the best option for PWM converters, thus it may work in discontinuous current mode (DCM) and this is not very suitable for high-power rating applications. Because of that ZVS + ZCS feature is not commonly used for PWM and FM is designed.

ZVS feature for the inverting network can be easily achieved with FM and the ZCS feature for the rectifier switches can also be achieved if there is no filter inductor at the output side.

# 2.3 LLC RESONANT HALF – BRIDGE CON-VERTER

A general description about resonant converters has been proposed previously. A suitable converter for unidirectional operation flow applications is half-bridge LLC Resonant Converter as demonstrated in (4), (5), (1) and (3).

A design procedure of LLC Resonant Converters is presented here. It is suitable for high-voltage and high-frequency applications and allows the output voltage regulation against variations from light- to full-loaded conditions. This section describes a typical LLC resonant half-bridge converter with its operation mode, its parts and its relationship between the input and the output voltages.

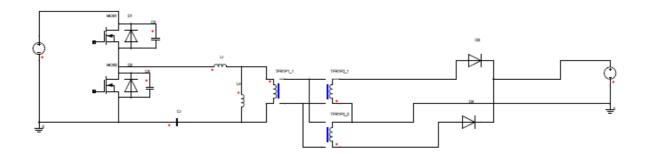

Figure 2.13 Half-Bridge LLC Resonant Converter

#### 2.3.1 Configuration

Figure 2.13 shows a typical topology of LLC resonant half-bridge converter. Two MOS-FET's are connected in a bridge configuration (MOS1, MOS2) connected to the resonant tank. Complementary mode with a fixed duty cycle (50%) is chosen to configure the converter. It also needs some dead time serving two purposes: Prevent short-circuits and the interval time used to charge / discharge the MOSFETs drain-to-source capacitance used for ZVS. A resonant capacitance ( $C_r$ ), and two inductances (the series resonant inductance,  $L_r$ , and the

transformer's magnetizing inductance,  $L_m$ ) form the resonant circuit or resonant tank. The transformer turn ratio is n and it provides electrical isolation. Thus, the energy between the resonant tank and the load circulates throw the transformer.

Two diodes constitute a rectifier to convert AC input to DC output and supply the load.

#### 2.3.2 Modeling

As seen previously, LLC converter has two resonant frequencies

$$\mathbf{f_0} = \frac{1}{2\pi\sqrt{\mathbf{L_r}\mathbf{C_r}}}$$

$$\mathbf{f_1} = \frac{1}{2\pi\sqrt{(\mathbf{L_{r+}L_m})\mathbf{C_r}}}$$

and most of the time LLC converter is designed to operate nearly of f<sub>0</sub>.

To design a converter for variable energy transfer and voltage regulation, a transfer function is very important. (6) shows how the gain formula is developed.

The relationship between the input voltage and the output voltage can be described by their ratio or gain

$$M_g = \frac{n \cdot V_0}{V_{in}/2}$$

For giving a gain depending on detailed values,  $f_0$  is selected as the base of normalization. Then the normalized frequency is expressed as

$$\mathbf{f_n} = \frac{\mathbf{f_{sw}}}{\mathbf{f_0}}.$$

An inductance ratio can be defined combining two inductances into one

$$L_{n} = \frac{L_{m}}{L_{r}}$$

and the quality factor of the series resonant circuit is defined as

$$\mathbf{Q_e} = \frac{\sqrt{\mathbf{L_r/C_r}}}{\mathbf{R_e}}.$$

With the help of these definitions, in (6) the voltage-gains is obtained as

$$\mathbf{M_g} = \left| \frac{\mathbf{L_n \cdot f_n^2}}{\left[ (\mathbf{L_n + 1}) \cdot \mathbf{f_n^2 - 1} \right] + \mathbf{j} \left[ (\mathbf{f_n^2 - 1}) \cdot \mathbf{f_n \cdot Q_e \cdot L_n} \right]} \right|$$

7

To understand the response of the resonant circuit Equation (7) is decisive. How changing  $f_n$  is possible to control  $M_g$  when  $L_n$  and  $Q_e$  are fixed.

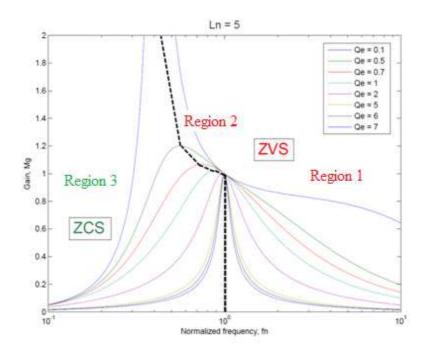

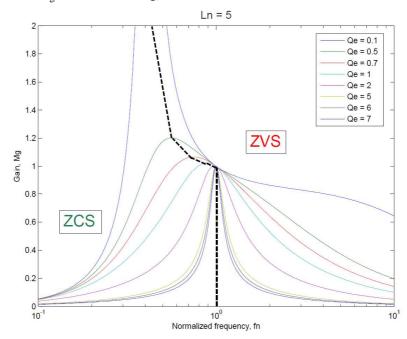

Figure 2.14 Plot of voltage-gain function (Mg) with Ln = 5

#### 2.3.3 Design considerations

Three requirements must be considered for the designing. At first, output voltage ( $V_{0\_min}$  and  $V_{0\_max}$ ) and input voltage ( $V_{in\_min}$  and  $V_{in\_max}$ ) are studied. The converter requirements define the maximum and the minimum values of the voltages.

$$\mathbf{M_{g\_min}} = \frac{\mathbf{n} \cdot \mathbf{V_{0\_min}}}{\mathbf{V_{in\ max}/2}}$$

and,

$$\mathbf{M_{g\_max}} = \frac{\mathbf{n} \cdot \mathbf{V_{0\_max}}}{\mathbf{V_{in\ min}/2}}$$

These Mg values are one of the limits for the operation zone.

The second requirement is  $Q_e$ , which is associated with the load current. The aim is to find the optimal value for each design, since a small  $Q_e$  makes the peak higher (Figure 2.14) while a gain curves have a larger frequency variation for a given gain adjustment ( $Q_e = 0$  is "no load" condition). A very low peak gain means a large  $Q_e$  which may not meet the design requirements.

Finally, low switching losses is one of the principle advantages of LLC topology and it is achieved through ZVS. As it is possible to see in Figure 2.14 and studied previously, ZVS is only reached on the right side of the resonant side of the resonant gain curves which needs to be checked in every designing process. This step is very important to achieve successfully the optimal designing.

#### 2.3.4 Selecting design parameters

#### • F<sub>sw</sub>, switching frequency

This parameter is previously defined considering different elements. For example, certain circuit components are more suitable for determined frequency. LLC has more benefits with higher switching frequency but other adverse factors appear when it is very high.

#### • n, transformer turns ratio

Assuming  $M_g = 1$ , n can be designed as

$$\mathbf{n} = \mathbf{M_g} \cdot \frac{\mathbf{v_{in}/2}}{\mathbf{v_0}}$$

#### • L<sub>n</sub> and Q<sub>e</sub>

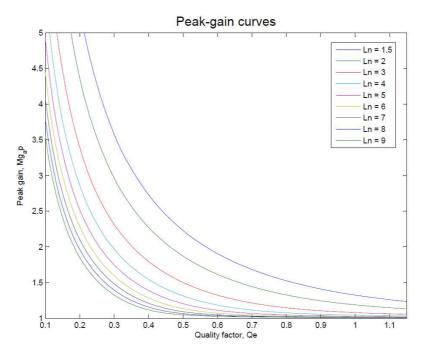

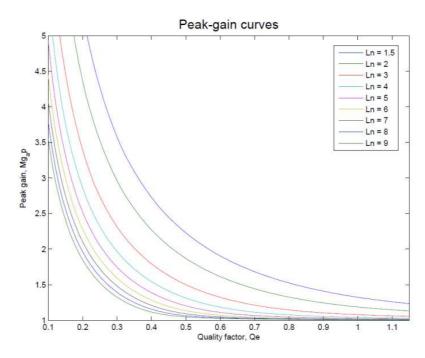

The most critical point in Figure 2.14 is the crossing point between  $M_{g_{max}}$  and the maximum value of  $Q_e$ . This point should be designed to prevent the operation zone entering in ZCS region. Following (6) a useful tool is to create the curve set up for the maximum  $M_g$  values for each  $Q_e$  curves, called  $M_{g_{ap}}$  as seen in Figure 2.15. Then Ln and  $Q_e$  can be selected, since  $M_{g_{ap}}$  is always higher than  $M_{g_{max}}$ .

Figure 2.15 Peak-gain curve

A small  $L_n$  keeps the operation zone out of the capacitance region because it makes the peak gain higher. As indicates Equation (5) it helps with ZVS but introduces higher magnetizing current and increases conduction losses.

Working in different load conditions is a main property, being no load condition ( $I_o$ =0,  $Q_e$  = 0) a critical operation point for high input voltage. Since the gain curves are determined by  $L_n$  and  $Q_e$  then  $L_n$  becomes the only design parameter. A value for  $L_n$  needs to be selected to provide a gain curve crossing over the horizontal lines defined by Equations (8) and (9).

#### • Re, Load resistance

Depends on the output-current and the output-voltage

$$\mathbf{R_e} = \frac{8 \cdot \mathbf{n^2}}{\pi^2} \cdot \frac{\mathbf{V_0}}{\mathbf{I_0}}$$

11

#### • Resonant circuit's parameters

$$C_{r} = \frac{1}{2 \cdot \pi \cdot Q_{e} \cdot f_{0} \cdot R_{e}}$$

12

$$\mathbf{L_r} = \frac{1}{(2 \cdot \pi \cdot \mathbf{f_0})^2 \cdot \mathbf{C_r}}$$

13

$$\mathbf{L_m} = \mathbf{L_n} \cdot \mathbf{L_r}$$

#### • Dead time

Enough dead time is an important requirement to assure ZVS in the converter and to avoid short circuit between the MOSFET's.

$$t_{dead} \ge n \cdot C_{eq} \cdot f_{sw} \cdot L_m$$

15

#### • Frequency range, $f_{n\_max}$ and $f_{n\_min}$

$F_{n\_max}$  and  $f_{n\_min}$  are obtained in  $M_g\text{-}f_n$  graph with  $M_{g\_max},\,M_{g\_min}\,\text{limits}$  and  $Q_e$  plot.

# 2.4 LLC RESONANT FULL – BRIDGE CON-VERTER

Full-bridge LLC Resonant Converter is more suitable converter for lower current values applications than half-bridge topology.

The operation mode, parts and relationship between the input and the output voltages for the full-bridge converter are described in this section.

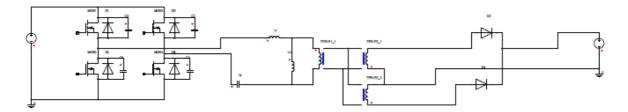

Figure 2.16 Full-Bridge LLC Resonant Converter

With the purpose of reducing the MOSFETs current in high-power applications, full-bridge topology is proposed with high-frequency galvanic isolation. This converter can improve power conversion efficiency using a zero-voltage transition feature.

#### 2.4.1 Configuration

In Figure 2.16 is seen a LLC resonant full-bridge converter. A bridge configuration is used here to connect two couples of MOSFETs (MOS1, MOS2, MOS3, and MOS4) to the resonant tank. A fixed duty cycle in complementary mode (50% MOS1 – MOS3 and MOS2 – MOS4) is chosen to configure the converter. Two purposes are taken in care to define the dead time. Prevent short-circuits and the interval time used to charge / discharge the MOSFETs drain-to-source capacitance used for ZVS.

Three elements form the resonant tank, resonant capacitance ( $C_r$ ), and two inductances (the series resonant inductance,  $L_r$ , and the transformer's magnetizing inductance,  $L_m$ ). The

transformer provides and important characteristic for the converter, electrical isolation. Half-bridge and full-bridge topology can be used for the rectifier to convert AC input to DC output and supply the load.

# 2.4.2 Modeling

The modeling is almost the same as in half-bridge topology (half-bridge modeling), equations (1) - (7). Only the relationship between the input voltage and the output voltage changes.

$$\mathbf{M_g} = \frac{\mathbf{n} \cdot \mathbf{V_0}}{\mathbf{V_{in}}}$$

16

# 2.4.3 Design considerations

The three requirements for the full-bridge converter are almost the same as the half-bridge (half-bridge design considerations). However, only the gain calculation is different in the process.

$$\mathbf{M_{g\_min}} = \frac{\mathbf{n} \cdot \mathbf{V_{0\_min}}}{\mathbf{V_{in \ max}}}$$

17

and,

$$\mathbf{M}_{\mathbf{g}_{\underline{\mathbf{max}}}} = \frac{\mathbf{n} \cdot \mathbf{V}_{\mathbf{0}_{\underline{\mathbf{max}}}}}{\mathbf{V}_{\mathbf{in}_{\underline{\mathbf{min}}}}}$$

18

# 2.4.4 Selecting design parameters

The process to select the optimal values for the resonant converter is similar to half-bridge topology (half-bridge selecting design parameters), equations (11) - (15). Only transformer turns ratio value is different

$$\mathbf{n} = \mathbf{M_g} \cdot \frac{\mathbf{v_{in}}}{\mathbf{v_0}}$$

22 2 RESONANT THEORY

# 2.5 CLLC BIDIRECTIONAL RESONANT CON-VERTER

CLLC converter is considered the most suitable option for bidirectional operation flow applications as demonstrated in (3) and (7), and a previous description has been proposed. This section describes a design procedure and steps for CLLC Resonant Converters.

Figure 2.17 Full-Bridge CLLC Resonant Converter

# 2.5.1 Configuration

The circuit configuration of the proposed converter (Figure 2.17) is very similar to the conventional LLC resonant converter (seen before at <u>LLC Configuration</u>) from the topology point of view, except for the additional resonant capacitor.

Primary and secondary side are both connected in full-bridge configuration (MOS1, MOS2, MOS3, and MOS4 to the resonant tank and MOS5, MOS6, MOS7, and MOS8 to the load) respectively.

The configuration changes depending on the direction of the power flow (Mode-1, Mode-2). In Mode-1, the power flows from left to right and in Mode-2 flows in the opposite direction. The converter is also configured in complementary mode with a fixed duty cycle (50%, 180° out of phase) for one side and a synchronous rectification (SR) for the other side. It also need some dead time as LLC converter.

The extra capacitor  $(C_{r2})$  in the right side makes this resonant tank different from LLC converter and allows working in bidirectional mode.

# 2.5.2 Modeling

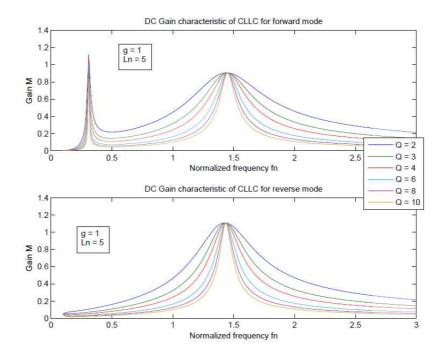

Mode-1 and Mode 2 have similar resonant properties, behavior over the switching frequency and even DC gain curves. However, as explained in (3) Mode-2 converter can be recognized as a LLC tank with an extra parallel resonant inductor. Mode-1 is more similar to the conventional SRC.  $C_{r2}$  acts like a dc blocking capacitor for both Modes.

For giving a gain depending on detailed values,  $f_0$  is selected as the base of normalization. Then the normalized frequency is expressed as

$$\mathbf{f_n} = \frac{\mathbf{f_{sw}}}{\mathbf{f_0}}.$$

An inductance ratio can be defined combining two inductances into one,

$$L_{n} = \frac{L_{m}}{L_{r}}$$

the quality factor of the series resonant circuit is defined as

$$\mathbf{Q_1} = \frac{\sqrt{\frac{\mathbf{L_r}}{\mathbf{C_{r1}}}}}{\mathbf{R_v}}$$

20

$$\mathbf{Q_2} = \frac{\sqrt{\frac{L_r}{C_{r2}}}}{R_v}$$

21

and the capacitance ratio is

$$\mathbf{g} = \frac{\mathbf{c_{r2}}}{\mathbf{c_{r1}}}$$

22

Based on the approach of fundamental mode approximation (FMA) (7), the equations of the dc gain for both modes can be expressed

$$M_{Mode-1} = \left| \frac{1}{\left[ \frac{1}{L_n} + 1 - \frac{1}{f_{n1}^2} \right] + j[Q_1 \cdot \left( \frac{1}{f_{n1}} - f_{n1} \right) + \frac{Q_1 \cdot (1 + L_n)}{(g \cdot L_n \cdot f_{n1})} - \frac{Q_1}{g \cdot L_n \cdot f_{n1}^3} \right]} \right|$$

23

24 2 RESONANT THEORY

$$M_{Mode-2} = \left| \frac{1}{\left[ 1 - \frac{1}{f_{n1}^2 \cdot Ln} \right] + j \left[ Q_2 \cdot \left( \frac{1}{f_{n2}} - f_{n2} \right) + \frac{Q_2 \cdot (1 + L_{n \cdot g})}{(L_n \cdot f_{n2})} - \frac{g \cdot Q_2}{L_n \cdot f_{n2}^2} \right]} \right|}$$

24

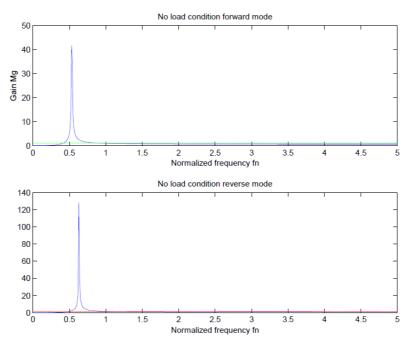

Figure 2.18 Comparative gain between Mode-1 and Mode-2

# 2.5.3 Design considerations

To alleviate the design difficulties, it is more suitable to start with the design of Mode-1 LLC resonant tank as seen in previous chapters and later Mode-2. It has the same design considerations and requirements as LLC converter.

# 2.5.4 Selecting design parameters

Only the step to obtain capacitance ratio is different from LLC converter process, seen in (10) – (15) equations (LLC converter design parameters).

- Fsw, switching frequency

- n, transformer turns ratio

- Ln and Q1

- Re, Load resistance

- Resonant circuit's parameters (Cr, Lr, Lm)

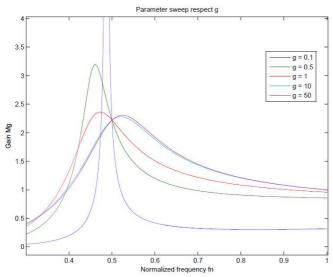

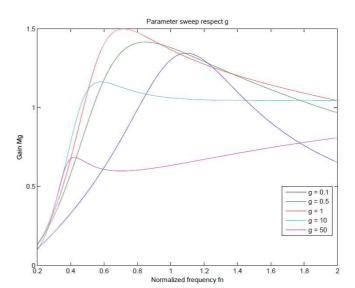

- Capacitance ratio, g

The optimal selection of parameter g depends on how similar the curves of the dc gain of the two modes are, under the condition of the same parameter g. A proper g should make the two dc gain curves similar as much as possible in shape and amplitude.

As parameter g having been known, the second resonant capacitor  $C_{r2}$  can be calculated.

Figure 2.19 Parameter sweep respect to g for forward mode

Figure 2.20 Parameter sweep respect to g for reverse mode

# 3 DESIGN AND SIMULATION

This chapter presents the design process and simulation of four automotive applications such as EV Auxiliary power supply, Galvanic Insulation for standard EV Onboard charger, EV Auxiliary power supply for MILD HEV and Galvanic Insulation for EV fast charger with optimal "Vehicle to grid" feature.

# 3.1 DESIGNED EV AUXILIARY POWER SUPPLY

In this chapter, a simulation of LLC Resonant Converters for EV auxiliary power supply applications is presented. A resonant converter has been designed to operate in an input voltage range of 240 – 550 V with an output voltage of 14.4 V. It will be verified in: its operation principle, its attribute of soft switching, and its parameters will be calculated. Within these design specifications, a performance analysis of the LLC converter has been conducted, comparing the results obtained at different working conditions.

# 3.1.1 Design steps

The specifications and main parameters are specified as follows.

o P<sub>0</sub>: 2500 W

o  $V_{in}$ : 240 – 550 V

o V<sub>out</sub>: 14.4 V

o  $I_0$ : 174 A

o  $f_{sw}$ : 120 kHz

With the required specifications, the design process is carried out:

#### • Determine transformer turn ratio

$$n = M_g \cdot \frac{V_{\text{in\_nom}}/2}{V_0} = 13.72$$

For transformer turns ratio calculation,  $\ensuremath{M_g}=1$  is used.

#### • Determine $M_{g\_min}$ and $M_{g\_max}$

$$M_{g_{-min}} = \frac{n \cdot V_{0_{-min}}}{V_{in max}/2} = 0.718$$

$$M_{g_{\text{max}}} = \frac{n \cdot V_{0_{\text{max}}}}{V_{\text{in_{min}}/2}} = 1.646$$

Maximum and minimum gains are obtained with the circuit requirements ( $V_{in}$  and  $V_{out}$ ) and the transformer turn ratio.

#### • Select Ln and Qe

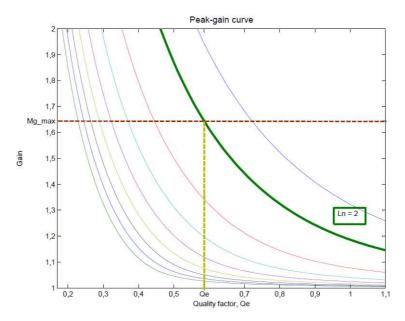

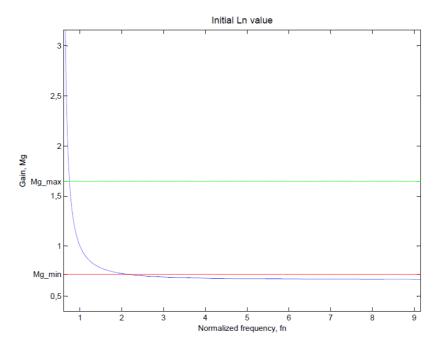

$L_n=2 \ {\rm is \ considered \ an \ optimal \ value \ for \ applications \ with \ no \ load \ condition \ and \ with}$   $M_{g\_max}, \ Q_e \ {\rm is \ obtained \ (Figure \ 3.1)}.$

$$Q_{e} = 0.57$$

Figure 3.1 Peak-gain curve for Ln = 2

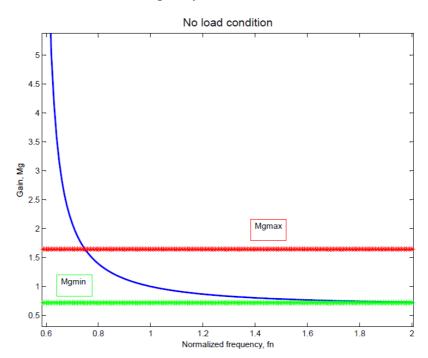

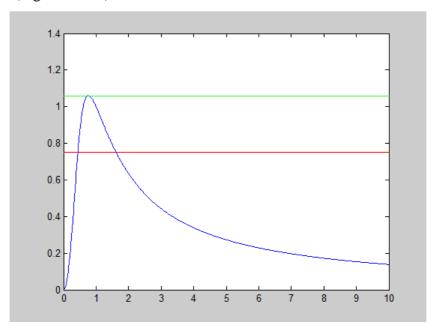

Properly behavior at no load working condition ( $Q_e=0$ ) is checked in Figure 3.2. The gain curve (blue) achieves  $M_{g\_min}$  (red) around  $f_n=1.8$  and the no load working condition is guaranteed with a reasonable frequency value.

Figure 3.2 No load condition for Ln = 2

#### • Determine the equivalent load resistance (Re) at full load

Determine the equivalent load resistance (R<sub>e</sub>) at full load

$$R_e = \frac{8 \cdot n^2}{\pi^2} \cdot \frac{V_0}{I_0} = 12.65 \Omega$$

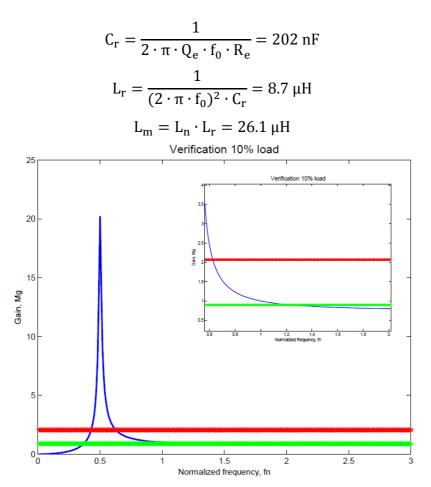

#### • Design resonant circuit's parameter

$$C_r = \frac{1}{2 \cdot \pi \cdot Q_e \cdot f_0 \cdot R_e} = 184 \text{ nF}$$

$$L_r = \frac{1}{(2 \cdot \pi \cdot f_0)^2 \cdot C_r} = 9.6 \text{ } \mu\text{H}$$

$$L_m = L_n \cdot L_r = 19.2 \text{ } \mu\text{H}$$

Resonant parameters are calculated here, but the designed working zone needs to be checked.

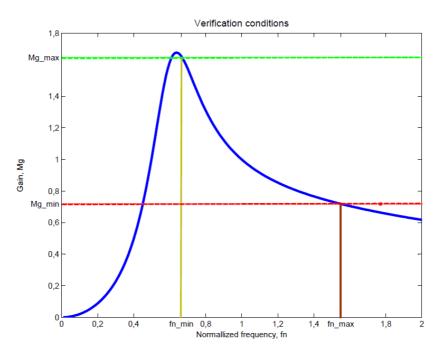

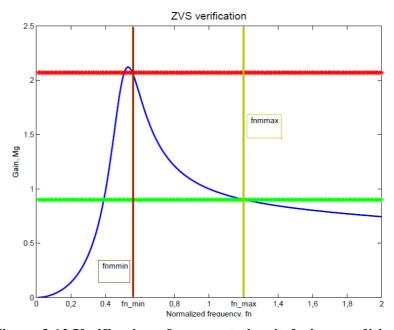

#### • Verify the resonant-circuit design

In the proposed LLC converter, input-voltage varies between 240 and 550 V for a constant 14.4 V output, with a variable frequency ( $f_{n_{min}}$ ,  $f_{n_{max}}$ ). Maximum and minimum  $M_g$  values have been calculated in the previous steps.

$$f_0 = \frac{1}{2\pi\sqrt{L_r C_r}} = 120 \text{ kHz}$$

$L_n = \frac{L_m}{L_r} = 2$

$Q_e = \frac{\sqrt{L_r / C_r}}{R_e} = 0.571$

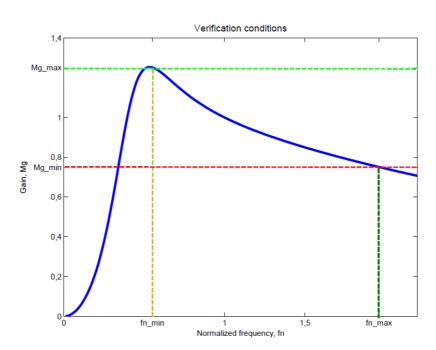

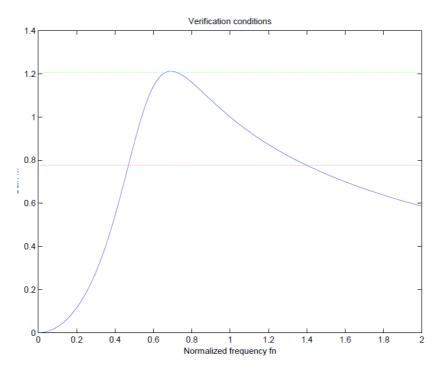

Working zone plotted in Figure 3.3 shows that ZVS condition is guaranteed and the values are within limits.

Figure 3.3 Verification of resonant-circuit design conditions

The frequency at no load (at  $M_{g\_min}$ ) is  $f_{n\_max} \cdot f_0 = 120 \cdot 1.55 = 186 \text{ kHz}$ The frequency at full load (at  $M_{g\_max}$ ) is  $f_{n\_min} \cdot f_0 = 120 \cdot 0.67 = 80.4 \text{ kHz}$  $F_{n\_max}$  and  $f_{n\_min}$  give the frequency limits for the converter.

#### Dead time

$$t_{dead} \ge n \cdot C_{eq} \cdot f_{sw} \cdot L_m = 221 \text{ ns}$$

A minimum dead time needs to be defined to avoid short-circuits and to assure ZVS.

For more information about LLC designing process consult <u>Annex 1</u>.

# 3.1.2 Simulation analysis and evaluation

For designing an LLC resonant half-bridge converter it is strongly recommended to use a computer simulation method. In this case, ANSYS Simplorer software is used for all the simulations in this project. In this section ZVS condition, resonant tank response, output

DATAMANSI

FOURTH

THANGE

THA

response and no load condition are presented to prove the designing.

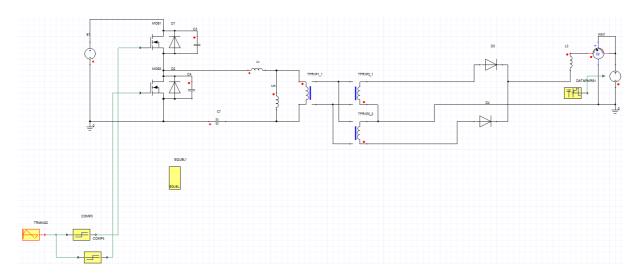

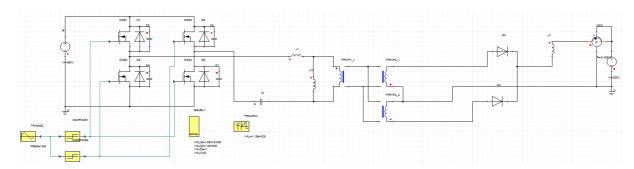

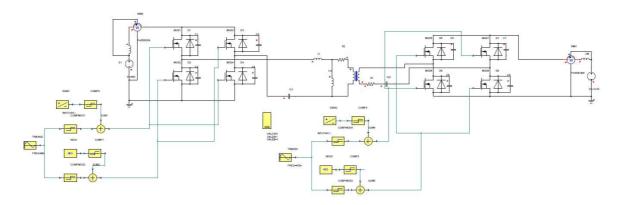

Figure 3.4 Simulated Half-Bridge LLC Resonant Converter

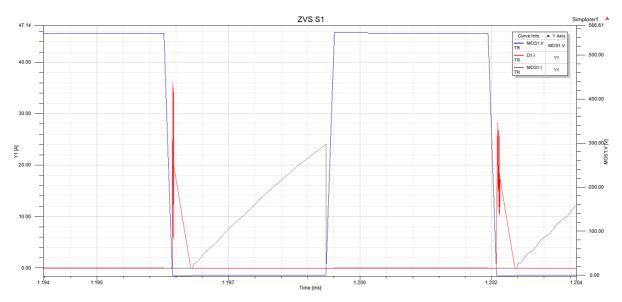

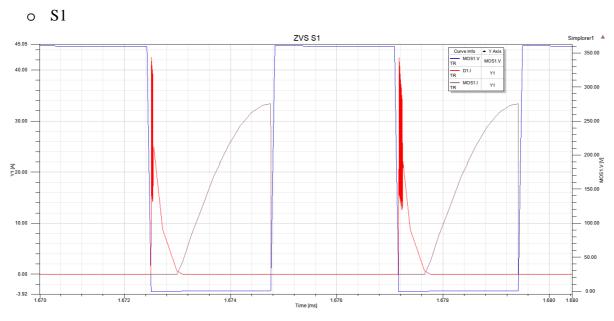

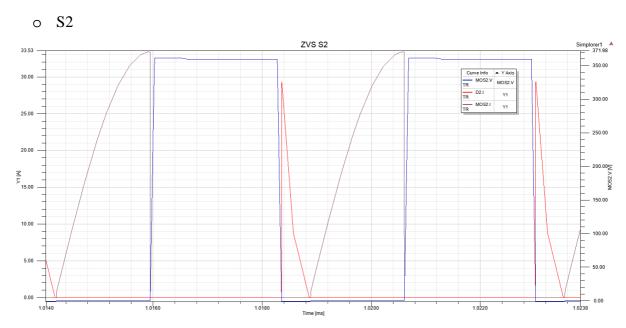

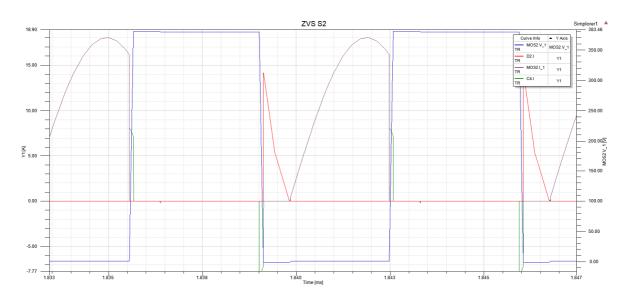

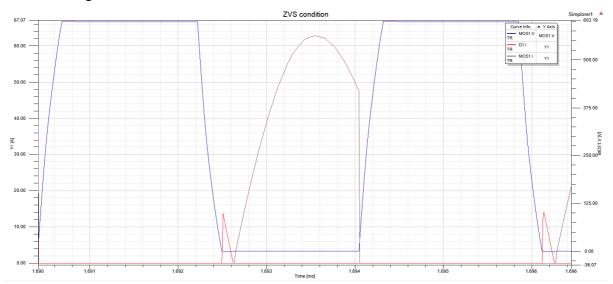

#### 3.1.2.1ZVS condition

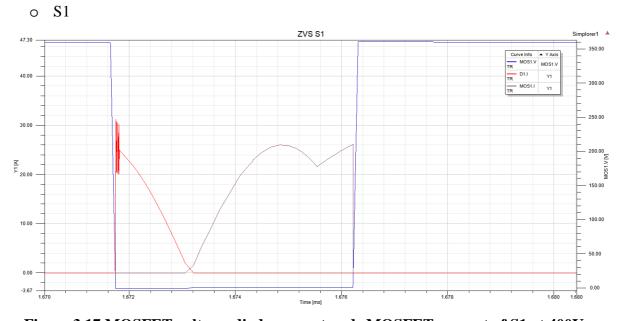

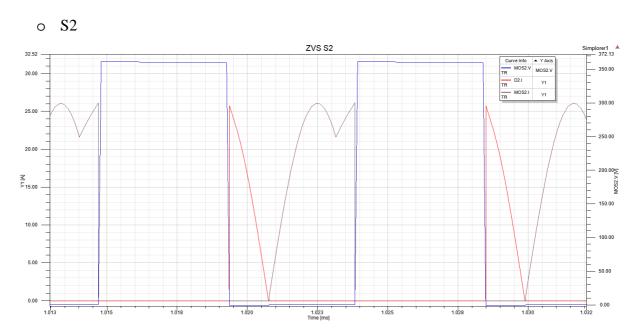

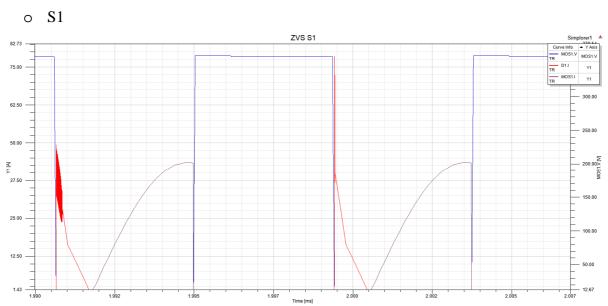

In this point, ZVS condition will be shown when the converter works at maximum input voltage, 550V.

As it is seen in Figure 3.5 and Figure 3.6, ZVS condition is achieved for both MOSFETs. When MOSFET starts to flow the current (purple), it does not see any voltage (blue), otherwise Diode is flowing the current (red). During the switching off, a progressive increasing of the voltage in MOSFET is produced.

o S1

Figure 3.5 MOSFET voltage, diode current ands MOSFET current of S1

Figure 3.6 MOSFET voltage, diode current ands MOSFET current of S2

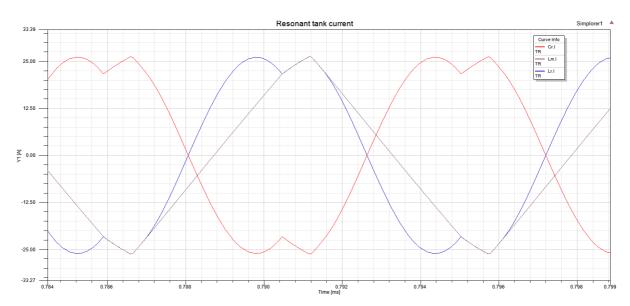

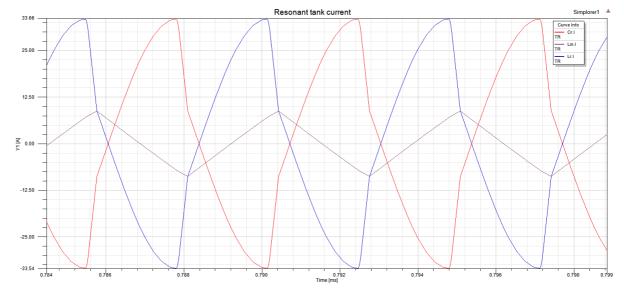

# 3.1.2.2Resonant tank response

Resonant tank current is shown in Figure 3.7 and Figure 3.8 to show soft flowing of the current in the resonant tank.

#### • 550 V

Figure 3.7 Resonant tank current at 550 V

#### • 240 V

Figure 3.8 Resonant tank current at 240 V

The current in the resonant tank is higher for the minimum input voltage. Same as in the MOSFETs.

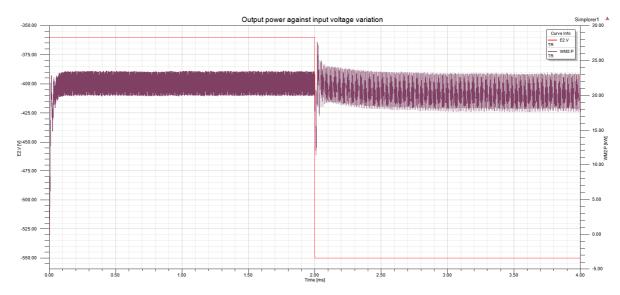

#### 3.1.2.3 LLC converter response

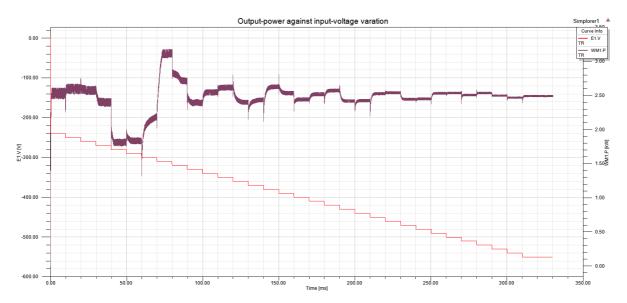

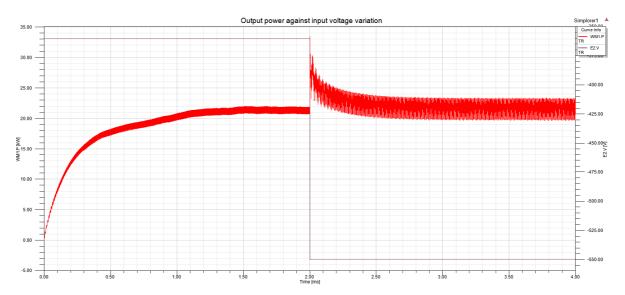

In Figure 3.9 is possible to see how the converter controls the output-power (purple) when an input voltage (red) variation between the maximum and the minimum values (and some intermediate values) is produced. In Figure 3.10 a sweep of whole input voltage is done between 240 V and 550 V.

Figure 3.9 Output-power response against input-voltage variation

Figure 3.10 Output-power response against input-voltage variation

Simulated converter responses against input-voltage variation through a feed-forward control, using a look-up table previously obtained. It causes that the converter spends a little time re-controlling the output power. A close-control can be a solution to avoid it.

To make clearer that the required output power is achieved, an output filter is used. Analyzing Figure 3.10, some values from the table are not good obtained since the output power (purple) does not give the expected values between 30 - 90 ms.

# 3.1.3 Converter response against 10% load

ZVS is an essential property, for this reason a method to guarantee ZVS at 10% load is presented.

For some applications it is essential to work in different load conditions, such as an auxiliary power supply. Work with 10% load changes conditions

$$R_e(10\% \text{ load}) = \frac{8 \cdot n^2}{\pi^2} \cdot \frac{V_0}{I_0} \cdot 10 = 126.5 \Omega$$

$$Q_e(10\% \text{ load}) = \frac{\sqrt{L_r/C_r}}{R_e \cdot 10} = 0.0323$$

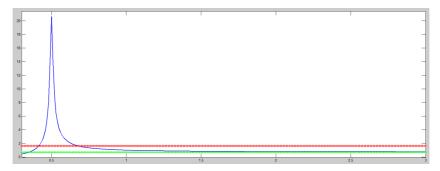

For high input voltage and low load conditions a proper response for the converter is more difficult. Figure 3.11 shows how the converter ( $L_n = 3$ ) cannot response properly at 10% load condition because  $f_{n \text{ max}}$  would be too higher.

Figure 3.11 Converter response under 10% load condition

A new designing step is proposed here to guarantee a proper behavior. (8) calculates M<sub>g\_min</sub>

value for a fixed  $V_{in}$ ,  $V_o$  and n. Fixing a higher  $M_{g\_min}$  and changing transformer turn ratio (n) allows the converter to work with the same input and output voltage. New values are obtained

$$M_{g\_min} = \frac{n \cdot V_{0\_min}}{V_{in\_max}/2} = 0.9$$

$M_{g\_max} = \frac{n \cdot V_{0\_max}}{V_{in\_min}/2} = 2.07$

$n = 17.187$

$L_n = 3$  is considered an optimal value and with  $M_{g_{\underline{}max}}$ ,  $Q_e$  is obtained.

$$Q_e = 0.33$$

Working zone plotted in Figure 3.12 shows that ZVS condition is guaranteed and the values are within limits.

Figure 3.12 Verification of resonant-circuit design conditions

The frequency at no load (at  $M_{g_min}$ ) is  $f_{n_max} \cdot f_0 = 120 \cdot 1.2 = 144 \text{ kHz}$

The frequency at full load (at  $M_{\text{g}\_\text{max}})$  is  $f_{n\_\text{min}} \cdot f_0 = 120 \cdot 0.56 = 67.2 \text{ kHz}$

Converter's response at 10% load condition is verified in Figure 3.13 and an acceptable value of  $f_{n_max}$  is obtained. New resonant circuit's parameters are calculated

Figure 3.13 Converter response under 10% load condition (with zoom)

# 3.2 GALVANIC INSULATION FOR STANDARD EV ONBOARD CHARGER RESONANT CONVERTER

Two resonant converters with an output power of 3600 W, which can be employed for an EV onboard charger, are designed here. The first converter has an output voltage range of 240 - 400 V within an input voltage of 360 V. The second resonant converter has an output voltage range of 360 - 530 V within an input voltage of 360 - 380 V.

#### 3.2.1 Model 1

As seen in the requirements, Model 1 has fixed input voltage and variable output voltage between 240 – 400 V. No load condition is not required for Model 1.

#### 3.2.1.1 Design steps

The specifications and main parameters of the converter are:

o P<sub>0</sub>: 3600 W

o V<sub>in</sub>: 360 V

o V<sub>out</sub>: 240 - 400 V

o I<sub>0</sub>: 11.25 A

o  $f_{sw}$ : 150 kHz

With the required specifications, the design process is carried out:

#### • Determine transformer turns ratio

$$n = M_g \cdot \frac{V_{in}/2}{V_{0\_nom}} = 0.56$$

$M_g = 1$  is assumed to calculate the transformer turn ratio.

#### • Determine Mg\_min and Mg\_max

$$M_{g_{min}} = \frac{n \cdot V_{0_{min}}}{V_{in}/2} = 0.75$$

$$M_{g_{max}} = \frac{n \cdot V_{0_{max}}}{V_{in}/2} = 1.25$$

Input voltage is always 360 V and the gains only vary depending on the output voltage.

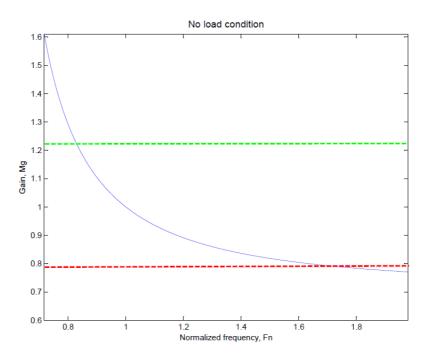

#### • Select Ln and Qe

No load condition is not required for Model 1 and  $L_n = 5$  is considered an optimal value for applications without no load requirements.  $Q_e$  is obtained with  $M_{g_max}$ .

$$Q_e = 0.465$$

Figure 3.14 Peak-gain curve for Ln = 5

#### • Determine the equivalent load resistance (Re)

$$R_e = \frac{8 \cdot n^2}{\pi^2} \cdot \frac{V_0}{I_0} = 7.3 \Omega$$

#### • Design resonant circuit's parameter

$$\begin{aligned} C_r &= \frac{1}{2 \cdot \pi \cdot Q_e \cdot f_0 \cdot R_e} = 312 \text{ nF} \\ L_r &= \frac{1}{(2 \cdot \pi \cdot f_0)^2 \cdot C_r} = 3.6 \text{ } \mu\text{H} \\ L_m &= L_n \cdot L_r = 18 \text{ } \mu\text{H} \end{aligned}$$

Theoretical values of the resonant parameters are used.

#### • Verify the resonant-circuit design

Assumed values are recalculated through equations.

$$f_0 = \frac{1}{2\pi\sqrt{L_rC_r}} = 150 \text{ kHz}$$

$$L_n = \frac{L_m}{L_r} = 5$$

$$Q_e = \frac{\sqrt{L_r/C_r}}{R_e} = 0.465 \text{ (at full load)}$$

These values are the same because theoretical values for the resonant parameters are used. Working zone plotted in Figure 3.15 shows that ZVS condition is guaranteed and the values are between limits.

Figure 3.15 Verification of resonant-circuit design conditions

Frequency at no load (at  $M_{g\_min}$ ) is  $f_{n\_max} \cdot f_0 = 150 \cdot 1.96 = 294 \text{ kHz}$ Frequency at full load (at  $M_{g\_max}$ ) is  $f_{n\_min} \cdot f_0 = 150 \cdot 0.55 = 82.5 \text{ kHz}$ The frequency limits for the converter are distinct by  $f_{n\_max}$  and  $f_{n\_min}$ .

#### Dead time

$$t_{dead} \ge n \cdot C_{ea} \cdot f_{sw} \cdot L_m = 10.6 \ ns$$

A minimum dead time needs to be defined to avoid short-circuits and to assure ZVS.

For more information about LLC designing process consult <u>Annex 1</u>.

# 3.2.1.2 Simulation analysis and evaluation

As in previous chapter, ANSYS Simplorer software is used for the simulation. ZVS condition, resonant tank response and output response are shown in this chapter to demonstrate the designing process.

Figure 3.16 Simulated Half-Bridge LLC Resonant Converter

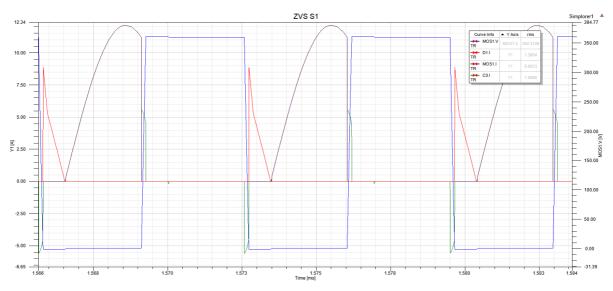

#### 3.2.1.2.1 ZVS condition

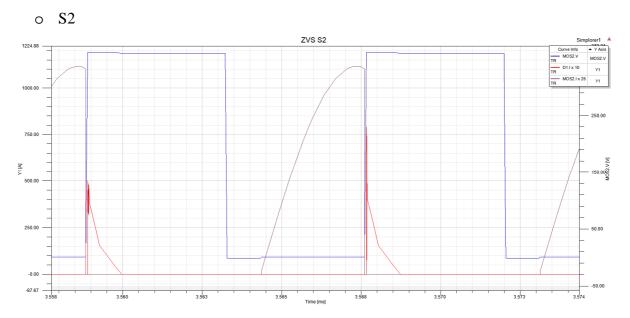

ZVS condition will be shown in both limits of the frequency range in this point.

#### • 400 V

Current diodes, MOSFETs voltage and current are shown in Figure 3.17 and Figure 3.18 for maximum output voltage (400 V) in S1 and S2.

Figure 3.17 MOSFET voltage, diode current ands MOSFET current of S1 at 400V

Figure 3.18 MOSFET voltage, diode current ands MOSFET current of S2 at 400V

#### • 240 V

Current diodes, MOSFETs voltage and current are shown in Figure 3.17 and Figure 3.18 for minimum output voltage (240 V) in S1 and S2.

Figure 3.19 MOSFET voltage, diode current ands MOSFET current of S1 at 240V

Figure 3.20 MOSFET voltage, diode current ands MOSFET current of S2 at 240V

In S1 for maximum and minimum voltage, the diodes flow some noisy current during the current peak. The simulation model should be studied detailed to propose a model which avoids this noise.

ZVS is achieved for both output voltage and for both MOSFETs.

#### 3.2.1.2.2 Resonant tank response

Different tank waveforms are presented in Figure 3.21 and Figure 3.22 to show circuit's behavior under limits of the frequency range condition.

Figure 3.21 Resonant tank current at 400 V

Figure 3.22 Resonant tank current at 240 V

It is seen how the current in the magnetizing inductance is higher for maximum output voltage (400 V). It means that the converter controls the current in the secondary side to keep the output power constant.

#### 3.2.1.2.3 LLC converter response

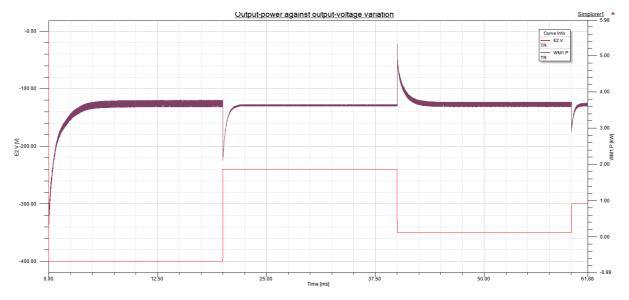

Figure 3.23 shows how the converter controls the output-power (purple) when output-

voltage (red) variation is produced. The output voltage varies between maximum (400 V) and minimum (240 V) values (and intermediates).

Figure 3.23 Output-power response against output-voltage variation

A feed-forward control using a look-up table previously obtained has been used to control the converter against the input-voltage variations. It causes that the converter spends a little time re-controlling the output power. A solution to avoid this could be a close-control. To make clearer that the required output power is achieved, an output filter is used.

#### 3.2.2 Model 2

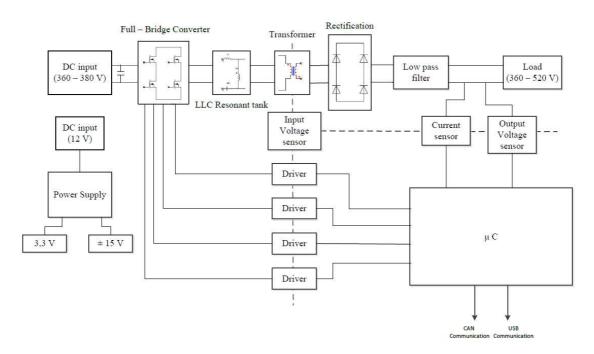

Model 2 is designed in half-bridge and full-bridge topologies, due to the currents in half-bridge topology are considered too high after having analyzed the simulation results. For hardware design, full-bridge topology currents are considered more suitable.

#### 3.2.2.1 Design steps for Half-Bridge topology

Main parameters and specifications are listed here:.

o P<sub>0</sub>: 3600 W

o  $V_{in}$ : 360 – 380 V

o  $V_{out}$ : 360 - 520 V

o I<sub>0</sub>: 8.1 A

o f<sub>sw</sub>: 150 kHz

With the required specifications, the design process is carried out:

#### • Determine transformer turn ratio

$$n = M_g \cdot \frac{V_{in\_nom}/2}{V_0} = 0.42$$

For transformer turns ratio calculation,  $M_{\rm g} = 1$  is used.

#### • Determine $M_{g\_min}$ and $M_{g\_max}$

$$M_{g_{\perp}min} = \frac{n \cdot V_{0_{\perp}min}}{V_{in max}/2} = 0.7877$$

$$M_{g_{max}} = \frac{n \cdot V_{0_{max}}}{V_{in_{min}}/2} = 1.224$$

In half-bridge Model 2 the gains vary depending on the output and the input voltage.

#### • Select Ln and Qe

$L_n$  = 2.5 (red) is considered an good value for applications with no load requirements. Entering with  $M_{g_{max}}$  (brown) in Figure 3.24,  $Q_e$  is obtained.

$$Q_{e} = 0.78$$

Peak-gain curve

1,9

1,6

1,7

1,6

1,4

1,3

Mg\_max

1,1

0,2

0,3

0,4

0,5

0,6

0,7

Qe

0,9

1

1

Normalized frequency, fn

Figure 3.24 Peak-gain curve for Ln = 2.5

In Figure 3.25 no load ( $Q_e=0$ ) working condition is checked. The gain curve (blue) achieves  $M_{g\_min}$  (red) around  $f_n=1.7$  and the no load working condition is guaranteed with a reasonable frequency value.

Figure 3.25 No load condition for Ln = 2.5

Determine the equivalent load resistance (Re) at full load

$$R_e = \frac{8 \cdot n^2}{\pi^2} \cdot \frac{V_0}{I_0} = 7.706 \Omega$$

Design resonant circuit's parameter

$$\begin{split} C_r &= \frac{1}{2 \cdot \pi \cdot Q_e \cdot f_0 \cdot R_e} = 176 \text{ nF} \\ L_r &= \frac{1}{(2 \cdot \pi \cdot f_0)^2 \cdot C_r} = 6.4 \text{ } \mu\text{H} \\ L_m &= L_n \cdot L_r = 16 \text{ } \mu\text{H} \end{split}$$

Resonant parameters are calculated here for half-bridge topology.

• Verify the resonant-circuit desig

Assumed values are recalculated through equations:

$$f_0 = \frac{1}{2\pi\sqrt{L_r C_r}} = 150 \text{ kHz}$$

$L_n = \frac{L_m}{L_r} = 2.5$

$Q_e = \frac{\sqrt{L_r / C_r}}{R_e} = 0.782$

Theoretical values for the resonant parameters are used and the recalculation is equal.

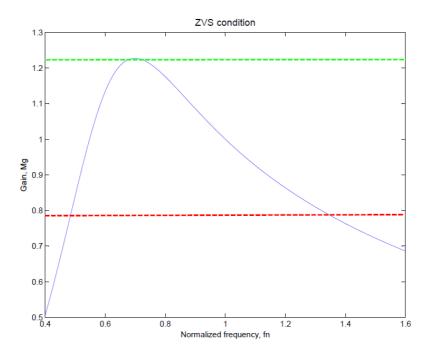

Working zone plotted in Figure 3.26 shows that ZVS condition is guaranteed and the values are within limits.

Figure 3.26 Verification of resonant-circuit design conditions

The frequency at no load (at  $M_{g\_min}$ ) is  $f_{n\_max} \cdot f_0 = 150 \cdot 1.335 = 200.25$  kHz. The frequency at full load (at  $M_{g\_max}$ ) is  $f_{n\_min} \cdot f_0 = 150 \cdot 0.725 = 108.75$  kHz.

#### • Dead time

$$t_{dead} \ge n \cdot C_{eq} \cdot f_{sw} \cdot L_m = 13.6 \text{ ns}$$

A minimum dead time needs to be defined to avoid short-circuits and to assure ZVS.

For more information about LLC designing process consult Annex 1.

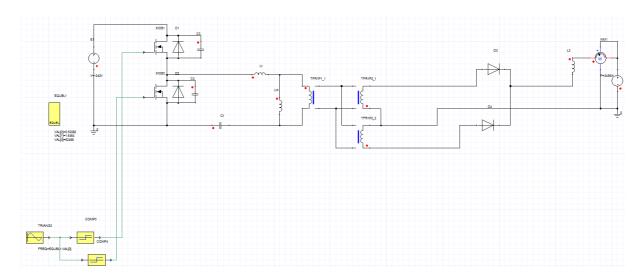

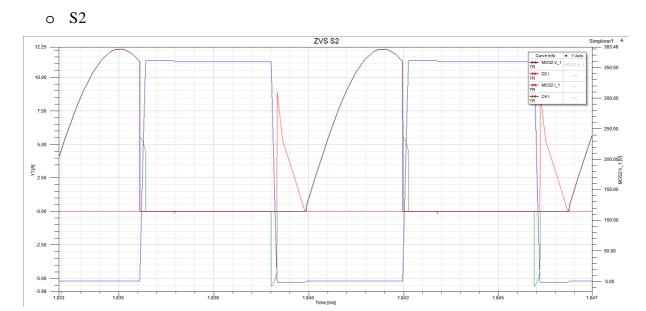

#### 3.2.2.2 Simulation analysis and evaluation of Half-Bridge topology

In this section ZVS condition, resonant tank response, output response and no load condition simulations (ANSYS Simplorer) are presented to prove the designing.

Figure 3.27 Simulated Half-Bridge LLC Resonant Converter

#### **3.2.2.2.1 ZVS condition**

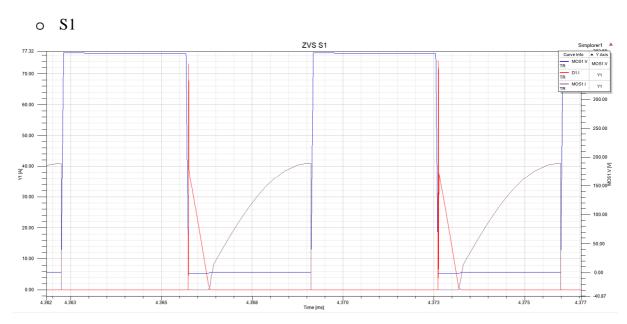

Converter response is shown in both limits of the frequency range ( $V_{in} = 360 \text{ V} - V_{out} = 360 \text{ V}$ ) to demonstrate ZVS.

#### • 520 V

As seen in Figure 3.28 and Figure 3.29, ZVS condition is achieved for the MOSFET (S1) when the converter works at maximum output voltage, 520 V.

Figure 3.28 MOSFET voltage, diode current ands MOSFET current of S1 at 520V

Figure 3.29 MOSFET voltage, diode current ands MOSFET current of S2 at 550V

#### • 360 V

ZVS condition is achieved for the MOSFET (S2) when the converter works at minimum output voltage, 360 V (Figure 3.30 and Figure 3.31).

Figure 3.30 MOSFET voltage, diode current ands MOSFET current of S1 at 360V

Figure 3.31 MOSFET voltage, diode current ands MOSFET current of S2 at 360V

Analyzing the converter response ZVS is achieved. However, as in other half-bridge LLC converter a noise is found in the diodes peak. The simulation model should be studied detailed to propose a model which avoids this noise.

#### 3.2.2.2.2 LLC converter response

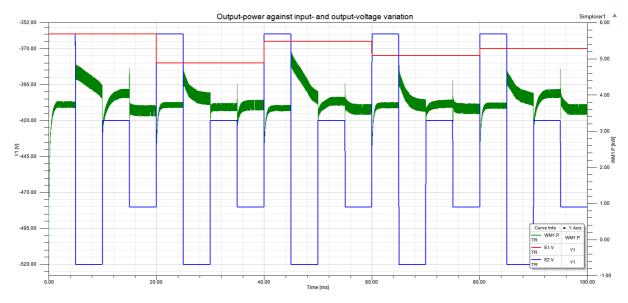

The converter controls the output-power (green) when the input voltage (red) and output voltage (blue) variation is produced as seen in Figure 3.32.

Figure 3.32 Output-power response against input/output-voltage variation

The step time for each variation is, in some cases, very short and the output power has not enough time to stabilize. Simulated converter responses against input-voltage variation through a feed-forward control, using a look-up table previously obtained. It causes that the converter spends time re-controlling the output power. A close-control can be a solution to avoid it. An output filter is used to make clearer that the required output power is achieved.

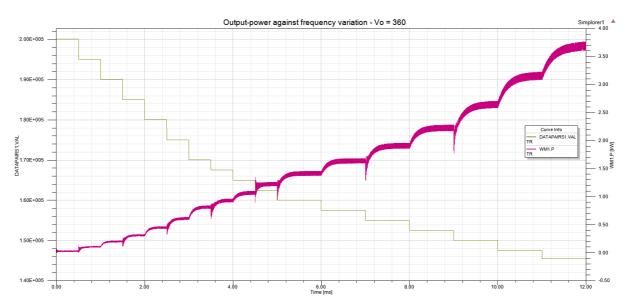

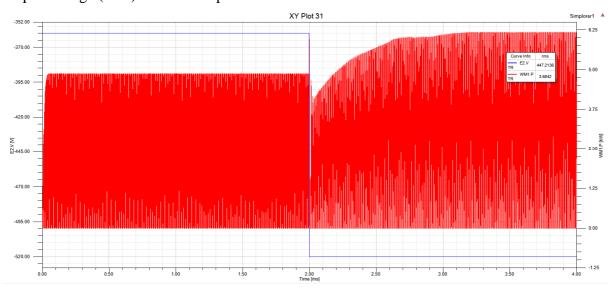

#### 3.2.2.2.3 Zero load condition

For some applications is essential to work in zero load condition, such as an EV onboard charger. Theoretical no load response has been previously demonstrated and simulating response is demonstrated in Figure 3.33 and Figure 3.34 for maximum and minimum output-voltage. It is possible to see how the converter is capable to give all the output power range (purple) between zero and maximum output power. A frequency sweep (green) is used to vary the frequency.

Figure 3.33 Output-power against frequency variation at Vo = 360 V

Figure 3.34 Output-power against frequency variation at Vo = 520 V

# 3.2.2.3 Design steps for Full-Bridge topology

After a detailed analysis of simulating MOSFETs response, the current is considered too high and a Full-Bridge topology is proposed.

The specifications and main parameters are specified as follows.

o P<sub>0</sub>: 3600 W

o  $V_{in}$ : 360 - 380 V

o  $V_{out}$ : 360 - 520 V

o I<sub>0</sub>: 8.1 A

o f<sub>sw</sub>: 150 kHz

With the required specifications, the design process is carried out:

#### • Determine transformer turn ratio

$$n = M_g \cdot \frac{V_{\text{in\_nom}}}{V_0} = 0.83$$

For transformer turns ratio calculation,  $\ensuremath{M_g}=1$  is used.

#### • Determine $M_{g\_min}$ and $M_{g\_max}$

$$M_{g\_min} = \frac{n \cdot V_{0\_min}}{V_{in\_max}} = 0.786$$

$$M_{g_{max}} = \frac{n \cdot V_{0_{max}}}{V_{in min}} = 1.222$$

The gain formula for half-bridge is different from full-bridge topology, it is divided by 2. However, the values are the same for both because the transformer turn ratio is also divided by 2 in half-bridge topology.

#### Select Ln and Qe

$L_n = 2.5$  is considered a good value for half-bridge and it is also used for full-bridge design.

$$Q_{e} = 0.78$$

Peak gain curve and no load condition are the same checking process and graphs than half-bridge design (no load and peak gain curve for half-bridge topology).

#### • Determine the equivalent load resistance (Re) at full load

$$R_e = \frac{8 \cdot n^2}{\pi^2} \cdot \frac{V_0}{I_0} = 30.716 \Omega$$

The transformer turns ratio is different for both topologies and the equivalent resistance is also different.

#### • Design resonant circuit's parameter

$$C_{r} = \frac{1}{2 \cdot \pi \cdot Q_{e} \cdot f_{0} \cdot R_{e}} = 44.3 \text{ nF} \rightarrow 47 \text{ nF}$$

$$L_{r} = \frac{1}{(2 \cdot \pi \cdot f_{0})^{2} \cdot C_{r}} = 25.4 \text{ }\mu\text{H} \rightarrow 36.3 \text{ }\mu\text{H}$$

$$L_{m} = L_{n} \cdot L_{r} = 63.5 \text{ }\mu\text{H} \rightarrow 98.1 \text{ }\mu\text{H}$$

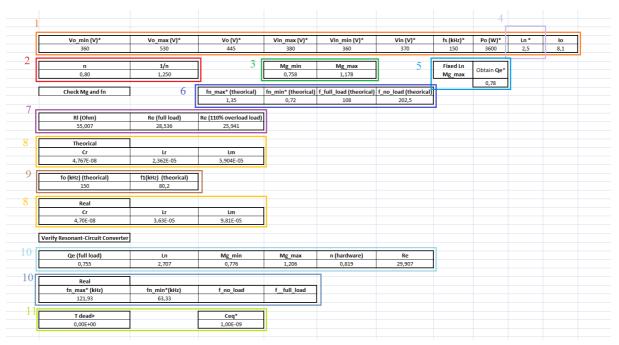

This design is used for hardware manufacture and the theoretical resonant parameters are not used because it is not possible to find a 44.3 nF capacitor. Normalized capacitor of 47 nF is used for the resonant capacitor. Most similar inductances values are obtained through the transformer design.

#### • Verify the resonant-circuit desig

With no theoretical resonant parameters the verification step is important to verify that the design is still suitable.

$$\begin{split} f_{n\_max} &= \frac{1}{2\pi\sqrt{L_rC_r}} = 121.93 \text{ kHz} \\ f_{n\_min} &= \frac{1}{2\pi\sqrt{(L_r + L_m) \cdot C_r}} = 63.33 \text{ kHz} \\ L_n &= \frac{L_m}{L_r} = 2.707 \\ Q_e &= \frac{\sqrt{L_r/C_r}}{R_c} = 0.755 \end{split}$$

Values are very similar to the theoretical ones and the working zone plotted in Figure 3.35 shows that ZVS condition is guaranteed and the values are within limits.

Figure 3.35 Verification of resonant-circuit design conditions

#### • Dead time

$$t_{dead} \ge n \cdot C_{eq} \cdot f_{sw} \cdot L_m = 26.51 \, ns \rightarrow 167 \, ns$$

The dead time for the full-bridge topology is quite different from the half-bridge because of the capacitors for the MOSFETs are also different. This capacitor is an important element to assure ZVS.

#### 3.2.2.4Simulation analysis and evaluation of Full-Bridge topology

ZVS condition and output response are shown in this chapter to demonstrate the designing process.

Figure 3.36 Simulated Full-Bridge LLC Resonant Converter

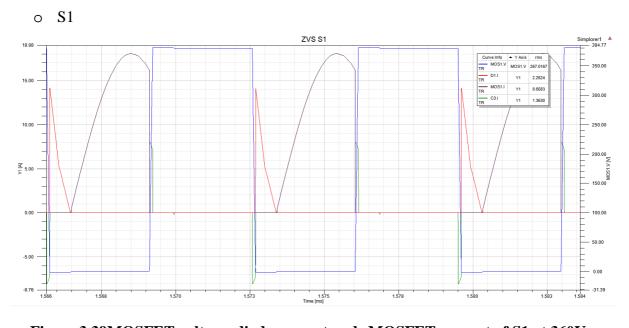

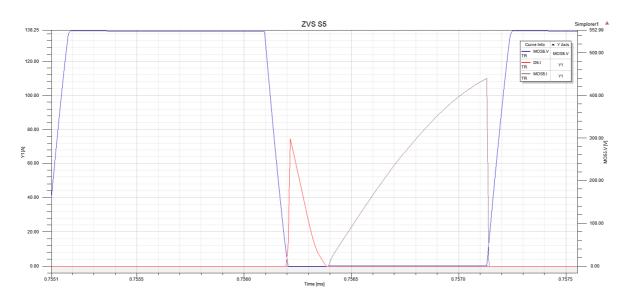

#### 3.2.2.4.1 ZVS condition

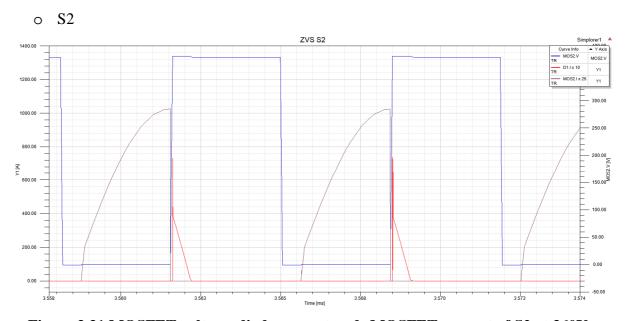

In this point, ZVS condition will be showed in both limits of the frequency range ( $V_{in} = 360$   $V - V_{out} = 520$  V;  $V_{in} = 380$   $V - V_{out} = 520$  V).

#### • 520 V

ZVS condition is shown in Figure 3.37 and Figure 3.38 for the maximum voltage, 520 V.

o S1

Figure 3.37 MOSFET voltage, diode current ands MOSFET current of S1 at 520V

Figure 3.38 MOSFET voltage, diode current ands MOSFET current of S2 at 520V

#### • 360 V

In Figure 3.39 and Figure 3.40 ZVS condition is shown for the minimum voltage, 3600 V.

Figure 3.39MOSFET voltage, diode current ands MOSFET current of S1 at 360V

o S2

Figure 3.40 MOSFET voltage, diode current ands MOSFET current of S2 at 360V

Capacitor current is shown in full-bridge Model 2 to show how the capacitors flow the current (only when de voltage grows up and decreases) and help to achieve ZVS.

#### 3.2.2.4.2 LLC converter response

In Figure 3.41 is possible to see how the converter controls the output power (red) when output voltage (blue) variation is produced.

Figure 3.41 Output-power response against output-voltage variation

For this converter an output inductance filter is not used. However, RMS value of the output power is calculated in the graphs. A close-control can be a solution to avoid that the converter spends time re-controlling the output power. Because of a feed-forward control with a look-up table has been used.

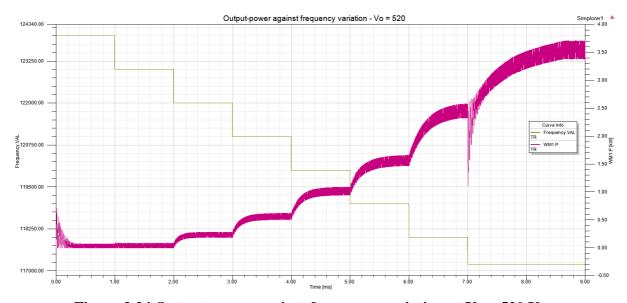

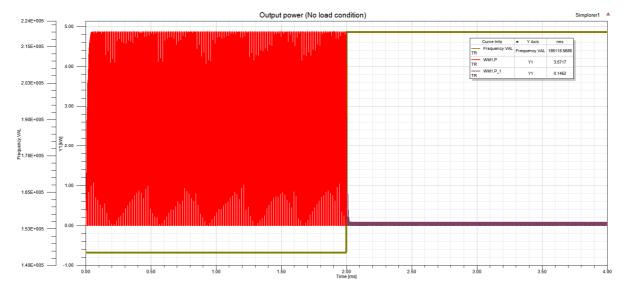

#### 3.2.2.4.3 Zero load condition

Zero load condition is also essential for full-bridge. No load simulation response is demonstrated in Figure 3.42. Maximum output power (3.6 kW) is given until 2 ms. At this point the frequency is varied to show how the converter can give the minimum power (0 kW) between 2-4 ms.

Figure 3.42 Output-power against frequency variation at Vo = 360 V

## 3.3 EV AUXILIARY POWER SUPPLY FOR MILD HEV

A bidirectional converter is proposed in this chapter to be design with CLLC topology. The application is EV auxiliary power supply for Mild HEV to operate with 48 V in one side, 14.4 V in the other side and a maximum output power of 2500 W in both directions.

#### 3.3.1 Design steps

The specifications and main parameters for forward mode and reverse mode are listed:

| Forward Mode (Mode-1): |         | Reverse Mode (Mode-2): |         |

|------------------------|---------|------------------------|---------|

| o P <sub>0</sub> :     | 2500 W  | P <sub>0</sub> :       | 2500 W  |

| o $V_{in}$ :           | 48 V    | V <sub>out</sub> :     | 48 V    |

| o $V_{out}$ :          | 14.4 V  | $V_{in}$ :             | 14.4 V  |

| $\circ$ $I_0$ :        | 173.6 A | $I_0$ :                | 52.1 A  |

| o f <sub>sw</sub> :    | 120 kHz | $f_{sw}$ :             | 120 kHz |

The first design steps are the same for CLLC converter as the LLC.

#### • Determine transformer turns ratio

$$n = M_g \cdot \frac{V_{in\_nom}}{V_0} = 3.33$$

$M_{\text{g}} = 1$  is assumed to calculate the transformer turn ratio for forward direction.

#### • Determine $M_{g\ min}$ and $M_{g\ max}$

$$M_{g\_Mode-1} = \frac{n \cdot V_0}{V_{in}} = 1$$

$$M_{g\_Mode-2} = \frac{\frac{1}{n} \cdot V_0}{V_{in}} = 1$$

The gain is 1 for both modes. Since the input and output voltage is fixed and the transformer turns ratio is inverted for different directions.

#### • Select Ln and Qe

$L_n = 2.5$  is considered an optimal value and with  $M_{g_{max}}$ ,  $Q_e$  is obtained.

$$Q_{e} = 0.4$$

• Determine the equivalent load resistance (Re) at full load

$$R_e = \frac{8 \cdot n^2}{\pi^2} \cdot \frac{V_0}{I_0} = 0.747 \ \Omega$$

• Design resonant circuit's parameter

$$\begin{split} C_r &= \frac{1}{2 \cdot \pi \cdot Q_e \cdot f_0 \cdot R_e} = 4.44 \ \mu F \\ L_r &= \frac{1}{(2 \cdot \pi \cdot f_0)^2 \cdot C_r} = 0.396 \ \mu H \\ L_m &= L_n \cdot L_r = 0.991 \ \mu H \end{split}$$

Until here the design process is the same as seen before in previous chapters.

#### • Capacitance ratio