# DESIGN AND SIMULATION OF A SINGLE-PHASE INVERTER WITH DIGITAL PWM

Bachelor Final Thesis

Industrial Technologies Engineering

Author: Elisa Braco Sola

Supervisor: Pr. Andreas Waldhorst

Krefeld, Germany. July 2016.

**Abstract**

The current project has as major aim the design of a single-phase inverter for educational

purposes. The main distinctive feature is the digital implementation of the PWM modulation.

Since the first Arduino board was developed on 2005, there has been a turning point on the

programming world, especially between non specialised users. With an intuitive software and a wide amount of applications, it is a highly recommended option for the first approach to digital

programming for students. For those reasons, this paper has the aim to apply this tool to ease the

PWM implementation on a single-phase inverter, substituting analogical circuitry.

Although nowadays it is possible to find integrated circuits with single – phase inverters, in order

to reinforce the educational approach, the circuit will be designed and built piece by piece. Thus,

it is easier to understand and visualize all the components required, as well as to check the

waveforms obtained on the internal elements.

To achieve those aims, a first complete theoretical analysis will be made, including its applications

and basic elements. Afterwards, the specific characteristics of the desired inverter will be defined,

allowing the computation and selection of the components required.

A fundamental part of the work relies on the programming of the PWM signal. For this reason, an

insight into the possibilities provided by the microcontroller will be made. Some options for codes

will be developed and the optimal for the application will be selected.

After the theoretical approach, the complete circuit will be simulated with the LTSpice software

and implemented in a protoboard. Some measurements will be also done in order to check the

performance of the device and its efficiency. Finally, a PCB with the complete circuit will be

developed.

Key words: single-phase inverter, PWM, Arduino.

i

Resumen

El presente proyecto tiene como objetivo principal el diseño de un inversor monofásico

con fines académicos. El rasgo más distintivo es la implementación digital de la modulación

PWM.

Desde que el primer Arduino fuera desarrollado en 2005, el mundo de la programación ha sufrido

un punto de inflexión, especialmente entre usuarios no especializados. Con un software intuitivo

y un amplio abanico de aplicaciones, es una opción muy recomendable para el primer contacto de

los estudiantes con la programación digital. Por ello, este documento pretende aplicar esta

herramienta para facilitar la implementación PWM en un inversor monofásico, sustituyendo la

tradicional circuitería analógica.

A pesar de que hoy en día es posible encontrar inversores monofásicos en circuitos integrados,

con el fin de reforzar el enfoque educacional, el circuito será diseñado y construido pieza a pieza.

Así, se facilita el entendimiento y visualización los componentes necesarios, así como la

comprobación de las formas de ondas en los elementos internos.

Para lograr estos objetivos, se realizará un primer análisis teórico, incluyendo aplicaciones y

elementos básicos. Posteriormente se definirán las características específicas del inversor

deseado, permitiendo así el cálculo y selección de los componentes necesarios.

Una parte fundamental del trabajo recae en la programación de la señal PWM. Por ello, se

contemplarán las posibilidades del microcontrolador al respecto. Diversas opciones para el código

serán consideradas y se seleccionará la mejor para la aplicación.

Tras el enfoque teórico, el circuito completo será simulado con el software LTSpice e

implementado en una protoboard. Asimismo se realizarán medidas con el fin de comprobar el

correcto funcionamiento del equipo y su eficiencia. Finalmente, el circuito será impreso en una

PCB.

Palabras clave: inversor monofásico, PWM, Arduino.

iii

# Acknowledgments

I would like to thank my supervisor Prof. Dr.-Ing. Andreas Waldhorst for the tracking and support throughout the project, as well as Alexander Lennartz and Lasse Wagner for all their advice and patience.

A special thanks goes also to the University of Applied Sciences — Hochschule Niederrhein for providing me the material required and allowing me to use its facilities, and to the Universidad Pública de Navarra for these four years of knowledge and training as engineer.

Elisa Braco

Krefeld, Germany. July, 2016.

# **Contents**

| СНАР | PTER 1: INTRODUCTION                                 | 1  |

|------|------------------------------------------------------|----|

| 1.1  | Objectives                                           | 1  |

| 1.2  | Scope                                                | 2  |

| СНАР | PTER 2: SINGLE-PHASE INVERTER                        | 3  |

| 2.1  | Definition                                           | 4  |

| 2.2  | DC - AC current                                      | 4  |

| 2.3  | Applications                                         | 5  |

| 2.4  | Output: modified sine wave and pure sine             | 6  |

| 2.5  | Elementary switching cell                            | 7  |

| 2.6  | Semiconductors. Selection of interrupters            | 8  |

|      | 2.6.1 Types of semiconductors                        | 8  |

|      | 2.6.2 Selection of semiconductors for an inverter    | 13 |

| 2.7  | Inverter topologies: Half - Bridge and Full - Bridge | 13 |

|      | 2.7.1 Half - Bridge                                  | 14 |

|      | 2.7.2 Full H-Bridge.                                 | 14 |

| 2.8  | PWM Modulation                                       | 15 |

|      | 2.8.1 Bipolar Modulation.                            | 16 |

|      | 2.8.2 Unipolar Modulation.                           | 18 |

| 2.9  | Driver                                               | 20 |

| 2.10 | ) Filter                                             | 21 |

| 2.11 | Other projects                                       | 22 |

| СНАР | PTER 3: DESIGN                                       | 23 |

| 3.1  | Context (features of the problem)                    | 24 |

| 3.2  | Performance criteria.                                | 24 |

|      | 3.1.1 Efficiency                                     | 24 |

|      | 3.1.2 Quality of the waveform                        | 25 |

|      | 313 Reactive Power                                   | 26 |

| 3.3  | Inverter topology                             | 28 |

|------|-----------------------------------------------|----|

| 3.4  | PWM Modulation. Switching frequency           | 29 |

|      | 3.4.1 PWM Modulation                          | 29 |

|      | 3.4.2 Switching frequency                     | 30 |

| 3.5  | Selection of semiconductors                   | 31 |

| 3.6  | Dead – times on the semiconductors            | 34 |

| 3.7  | Losses in semiconductors                      | 36 |

|      | 3.7.1 Analysis                                | 36 |

|      | 3.7.2 Calculation                             | 39 |

|      | 3.7.3 Power dissipation                       | 40 |

| 3.8  | Circuit elements selection                    | 42 |

|      | 3.8.1 Capacitors                              | 42 |

|      | 3.8.2 Inductances                             | 42 |

|      | 3.8.3 Filter                                  | 43 |

|      | 3.8.4 Output load                             | 44 |

| 3.9  | Driver                                        | 44 |

|      | 3.9.1 Input voltages                          | 46 |

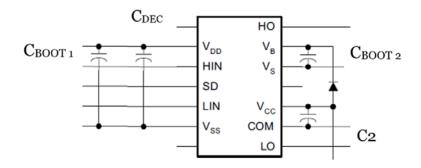

|      | 3.9.2 External elements                       | 48 |

| 3.10 | O Circuit protections                         | 50 |

|      | 3.10.1 Overvoltage protection                 | 51 |

|      | 3.10.2 Overcurrent protection                 | 51 |

|      |                                               |    |

| СНАІ | PTER 4: MICROCONTROLLER                       | 55 |

| 4.1  | Definition                                    |    |

| 4.2  | Timers                                        | 57 |

|      | 4.2.1 Clear Timer on Compare Match (CTC) Mode | 58 |

|      | 4.2.2 Fast PWM                                |    |

|      | 4.2.3 Phase correct PWM Mode                  | 59 |

| 4.3  | PWM                                           | 60 |

|      | 4.3.1 Calculation of the duty cycle           |    |

|      | 4.3.2 Interrupts                              |    |

|      | 4.3.3 PWM generation                          |    |

|      |                                               |    |

| СНА  | PTER 5: SIMULATION AND RESULTS                | 73 |

| 5.1  | Testing circuits                              |    |

| ~    |                                               |    |

|       | 5.1.1 Inverter gate                   | 74  |

|-------|---------------------------------------|-----|

|       | 5.1.2 Driver                          | 75  |

|       | 5.1.3 Half Bridge                     | 77  |

| 5.2   | Full H-Bridge                         | 78  |

|       | 5.2.1 Vs connection                   | 79  |

|       | 5.2.2 Optimal load                    | 80  |

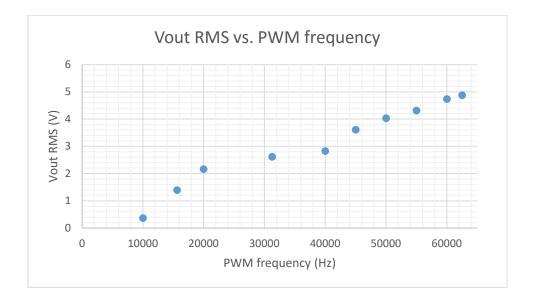

|       | 5.2.3 PWM frequency                   | 81  |

|       | 5.2.4 V <sub>DC</sub> input           | 84  |

|       | 5.2.5 Voltages on the MOSFETs         | 84  |

|       | 5.2.6 Output voltage                  | 86  |

|       | 5.2.7 Quality of the inverter         | 89  |

| 5.3   | PCB                                   | 91  |

|       |                                       |     |

| СНАР  | PTER 6: CONCLUSION                    | 92  |

| 6.1   | Objectives achieved                   | 93  |

| 6.2   | Further developments                  | 93  |

|       | 6.2.1 Efficiency                      | 93  |

|       | 6.2.2 Microcontroller                 | 94  |

|       | 6.2.3 Control                         | 94  |

| Refer | ences                                 | 96  |

|       |                                       |     |

| Apper | ndix A: Calculations                  | 99  |

| A.1   | •                                     |     |

| A.2   | Output inductance                     | 100 |

| A.3   | Filter                                | 103 |

| A.4   | Gate to source resistor               | 103 |

| A.5   | Snubber circuit                       | 104 |

|       | Heatsink                              |     |

|       | ndix B: Code                          |     |

|       | ndix C: Modes of Operation in Arduino |     |

| Apper | ndix D: Design Documents              | 112 |

# List of figures

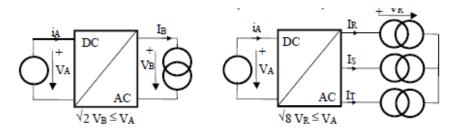

| 2.1:  | Single - phase and three – phase voltage inverters [1]                     | 4  |

|-------|----------------------------------------------------------------------------|----|

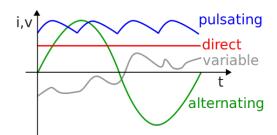

| 2.2:  | Direct and alternating current and voltage [2]                             | 4  |

| 2.3:  | Examples of applications. [3]                                              | 5  |

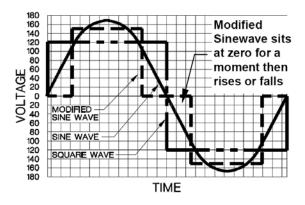

| 2.4:  | Square, modified and sine wave. [4]                                        | 6  |

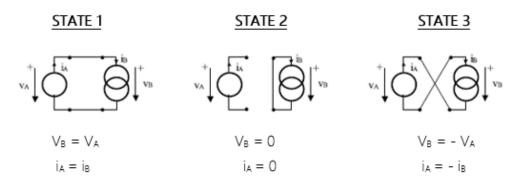

| 2.5:  | Connection states allowed [1]                                              | 7  |

| 2.6:  | Elementary switching cell.                                                 | 7  |

| 2.7:  | Symbol and structure of a diode [1]                                        | 8  |

| 2.8:  | Current-voltage characteristics for a diode [5]                            | 9  |

| 2.9:  | BJT symbol and structure [1]                                               | 9  |

| 2.10: | Structure and symbol of an N-Channel MOSFET [1]                            | 10 |

| 2.11: | Static behaviour of an N-Channel MOSFET [5]                                | 10 |

| 2.12: | Cross section of a VDMOS, showing an elementary cell [27]                  | 11 |

| 2.13: | Structure and symbol of an IGBT [1]                                        | 11 |

| 2.14: | Static behaviour of an IGBT [7]                                            | 12 |

| 2.15: | Selection of semiconductors regarding capacity and operation frequency [6] | 12 |

| 2.16: | Semiconductors chosen                                                      | 13 |

| 2.17: | Single – phase Half – Bridge voltage inverter. [7]                         | 14 |

| 2.18: | Single – phase Full H – Bridge voltage inverter. [7]                       | 15 |

| 2.19: | PWM waveforms and schematic.                                               | 15 |

| 2.20: | Analogic circuitry for bipolar modulation in LTSpice software              | 16 |

| 2.21: | Resume of bipolar modulation.                                              | 17 |

| 2.22: | Main waveforms of bipolar modulation. [1]                                  | 17 |

| 2.23: | Analogic circuitry for unipolar modulation in LTSpice software             |    |

|       | Resume of unipolar modulation                                              |    |

|       | Main waveforms of unipolar modulation. [1]                                 |    |

| 2.26: | Output waveform with bipolar modulation (up) and unipolar modulation       | 20 |

| 2.27: | Functional schematic of a driver [1]                                       | 20 |

|       | RC and LC low pass filters and waveforms.                                  |    |

| 3.1:  | Relation between Active, Reactive and Apparent Power [17]                  | 26 |

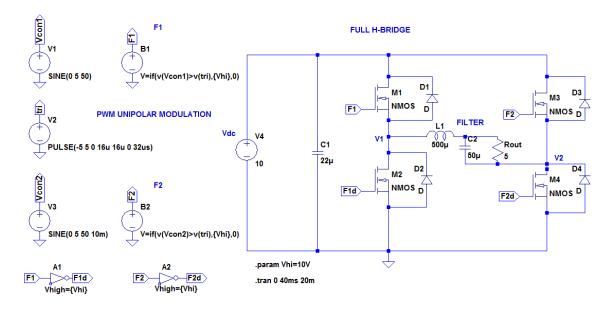

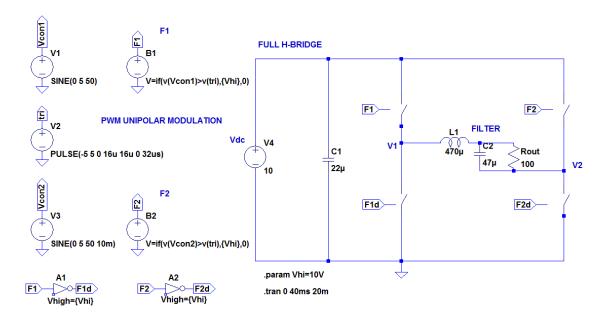

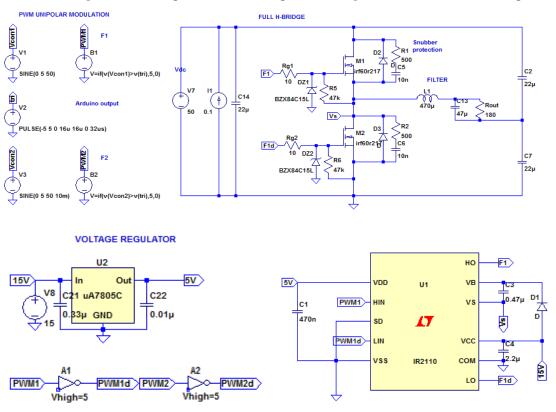

| 3.2:  | Full H-Bridge schematic with LTSpice software.                             | 28 |

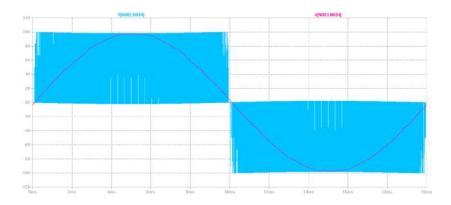

| 3.3:  | Output waveform with bipolar (left) and unipolar (right) modulation        | 29 |

| 3.4:   | Efficiency for f=20 kHz vs. Power [1]                                               | 30 |

|--------|-------------------------------------------------------------------------------------|----|

| 3.5:   | Schematic of Full H-Bridge applied for comparison between semiconductors            | 32 |

| 3.6:   | Output voltage waveform on ideal switchers (1), MOSFET (2) and IGBT (3)             | 33 |

| 3.7:   | IRF60B217 with TO-220AB package                                                     | 34 |

| 3.8:   | Error due to dead time in semiconductors [1]                                        | 35 |

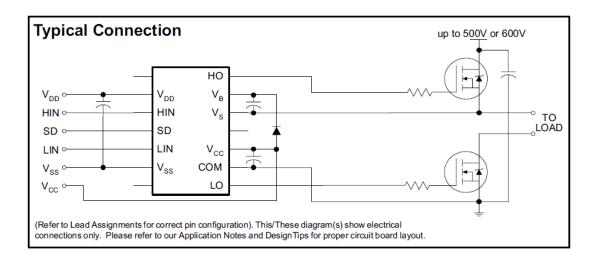

| 3.9:   | Block diagram of the IR2110. [18]                                                   | 35 |

| 3.10:  | Diode conducting model                                                              | 36 |

| 3.11:  | Model and waveforms of turning on (left) and off of the MOSFET [1]                  | 37 |

| 3.12:  | Capacitances on a MOSFET [1]                                                        | 37 |

| 3.13:  | Diode conducting model [1]                                                          | 38 |

| 3.14:  | Turn-off behaviour (a) and current curve, voltage and switching losses (b) [5]      | 38 |

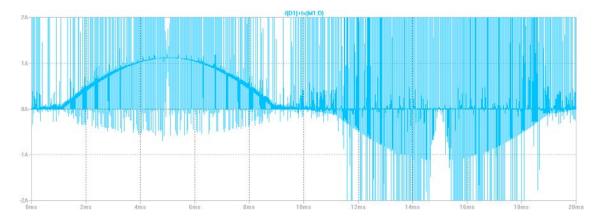

| 3.15:  | Current in a branch in one period (20ms)                                            | 39 |

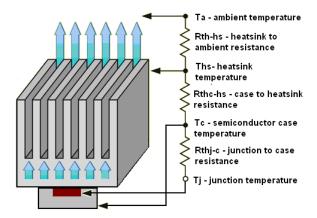

| 3.16:  | Schematic and electric circuit between silicon junction and ambient. [14]           | 41 |

| 3.17:  | Waveform of inductance current with Lout=160 µH                                     | 43 |

| 3.18:  | Waveform of inductance current with Lout=470 $\mu H$ .                              | 43 |

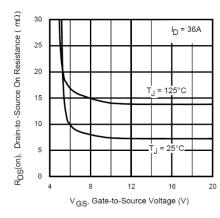

| 3.19:  | On – Resistance vs. Gate Voltage [17]                                               | 45 |

| 3.20:  | Typical connection of IR2110 [18]                                                   | 46 |

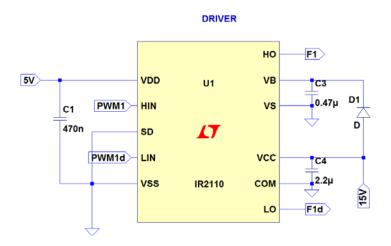

| 3.22:  | Complete scheme of the driver and external elements                                 | 48 |

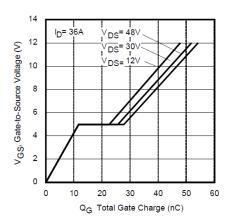

| 3.23:  | Typical Gate Charge vs. Gate-to-Source Voltage on IRF60b217 [17]                    | 48 |

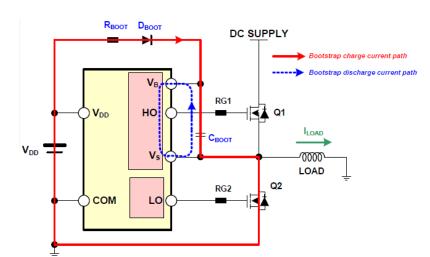

| 3.24:  | Current path on a bootstrap circuit [28]                                            | 49 |

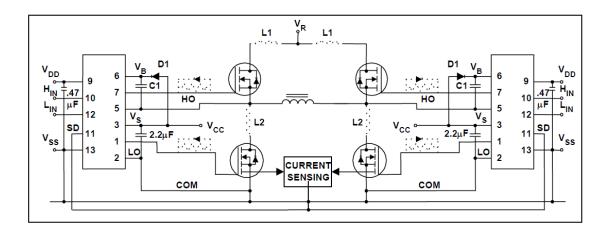

| 3.24:  | Typical implementation of an H-Bridge [19]                                          | 50 |

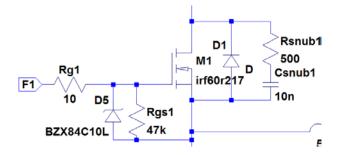

| 3.25:  | Complete scheme of MOSFETs protection                                               | 52 |

| 3.26:  | Equivalent circuit of a MOSFET showing components with greatest effect on switching | 53 |

| 4.1:   | Arduino UNO board                                                                   | 56 |

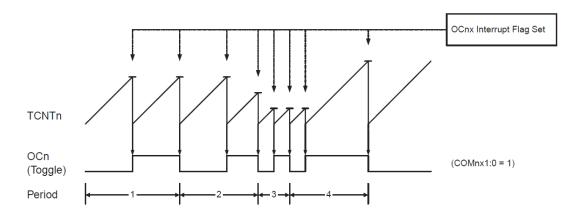

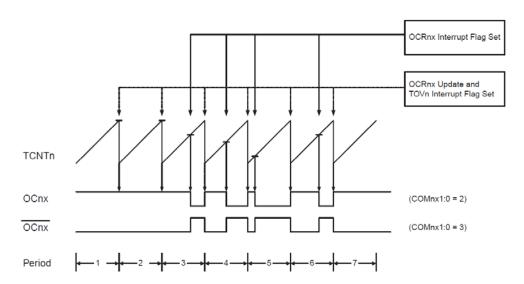

| 4.2:   | CTC Mode timing diagram [21]                                                        | 58 |

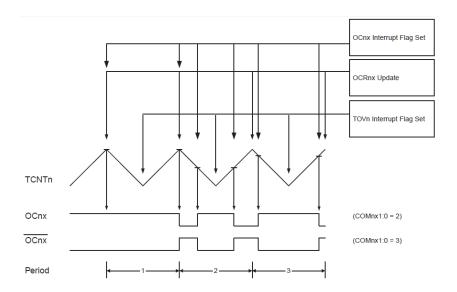

| 4.3:   | Fast PWM Mode timing diagram [22]                                                   | 59 |

| 4.4:   | Phase correct PWM Mode timing diagram [22]                                          | 60 |

| 4.5:   | PWM waveforms and schematic                                                         | 60 |

| 4.6:   | Extract code for sine computation.                                                  | 62 |

| 4.7:   | Extract code for Timer 2 configuration                                              | 64 |

| 4.8:   | Code for PWM generation with digitalWrite ()                                        | 65 |

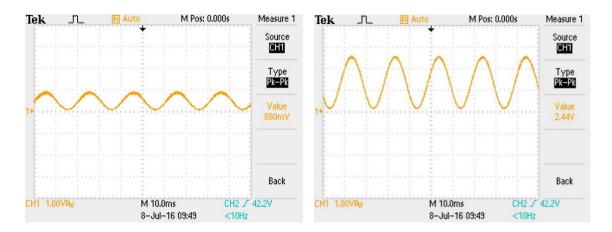

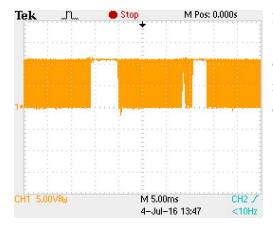

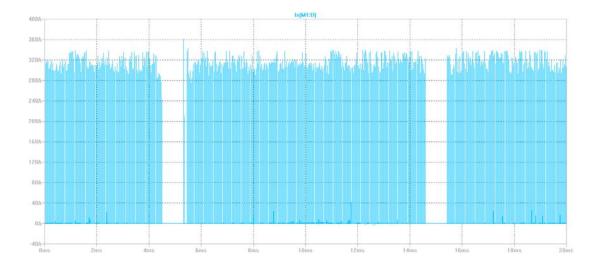

| 4.9:   | Output pin 9 waveform with analogWrite ()                                           | 66 |

| 4.10:  | Output pin 9 waveform with Code 1 filtered.                                         | 66 |

| 4.11:  | Extract code for Timer 1 configuration                                              | 68 |

| 4.12:  | Output waveforms for OCRnA and OCRnB with fast PWM and phase-correct PWM $\ldots$   | 69 |

| 4.13:  | Extract code of Interrupt Service Routine                                           | 69 |

| 4.14:  | Output pin 9 waveform.                                                              | 70 |

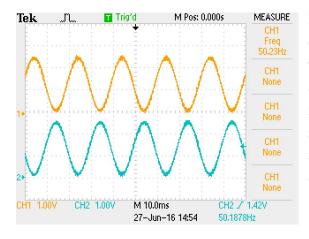

| 4.15:  | Output pin 9 and 10 waveform with Code 1 filtered                                   | 70 |

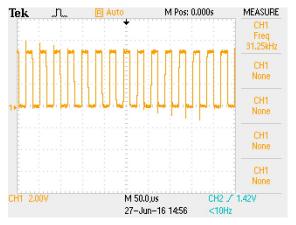

| 4. 16: | Output waveforms from Arduino with PWM frequencies of 31250 Hz and 62500 Hz.        | 71 |

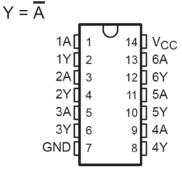

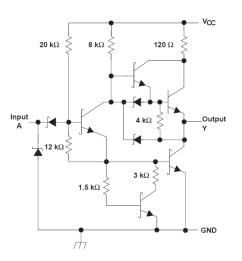

| 5.1:   | Pin layout and internal structure of 74LS04 [24]                                      | 74  |

|--------|---------------------------------------------------------------------------------------|-----|

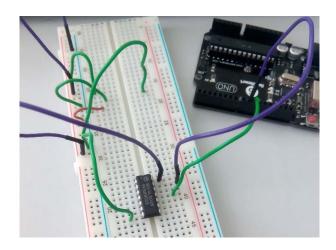

| 5.2:   | Test circuit for the inverter gate                                                    | 75  |

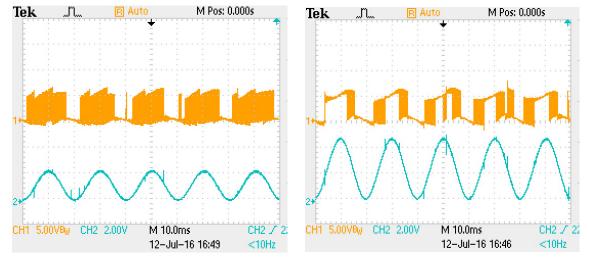

| 5.3:   | Output of the inverter gate with single input (left) and with both PWM inputs         | 75  |

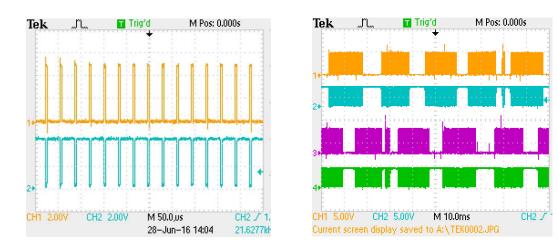

| 5.4:   | Testing schematic for IR 2110, based on [18]                                          | 76  |

| 5.5:   | Testing circuit for IR 2110                                                           | 76  |

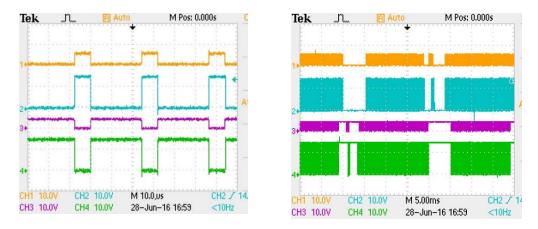

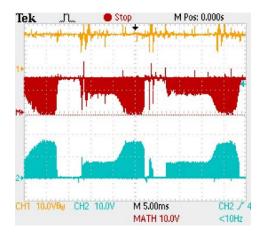

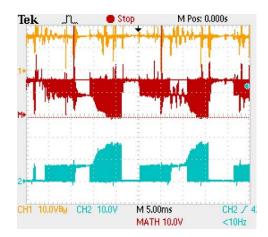

| 5.6:   | IR2110 HIN, HO, LIN and LO pins.                                                      | 77  |

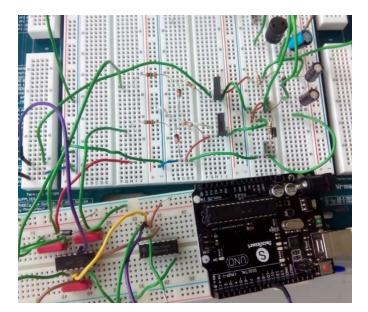

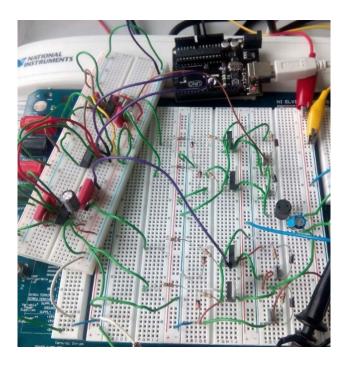

| 5.7:   | Schematic (up), picture and output waveform of half bridge test circuit               | 78  |

| 5.8:   | H-Bridge circuit                                                                      | 78  |

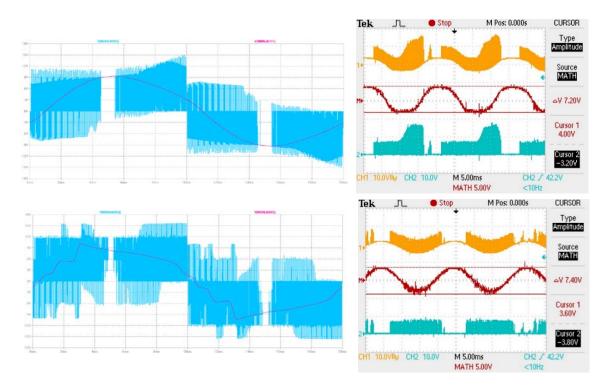

| 5.9:   | Simulated (left) and real output waveform for Vs connected to ground (top) and to the |     |

| midd   | le point of the bridge (bottom)                                                       | 80  |

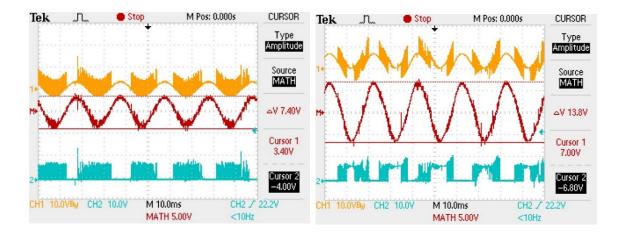

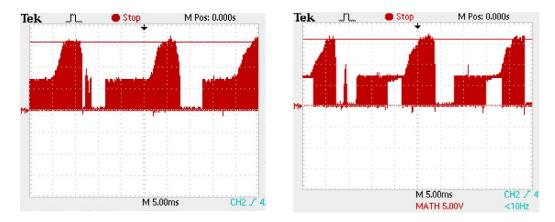

| 5.10:  | Output waveforms with R=10 $\Omega$ (left) and R=500 $\Omega$ (right)                 | 81  |

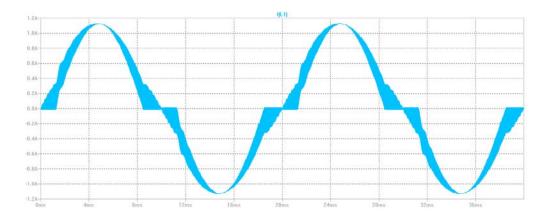

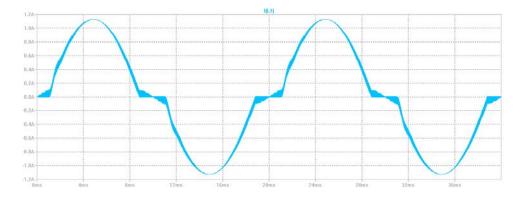

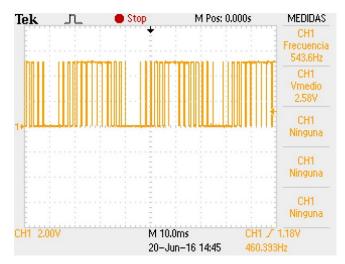

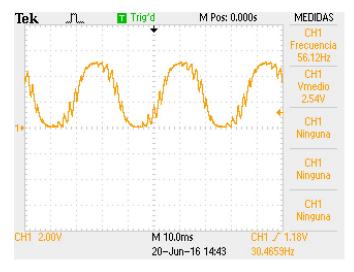

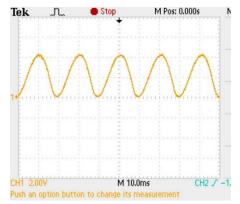

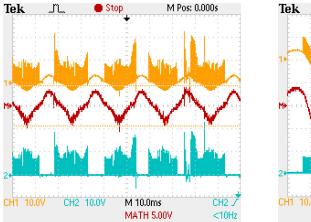

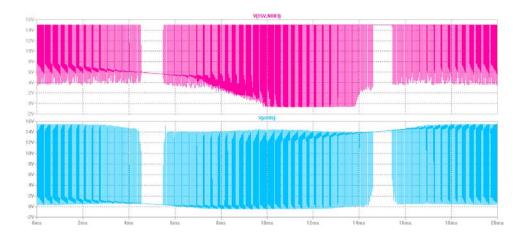

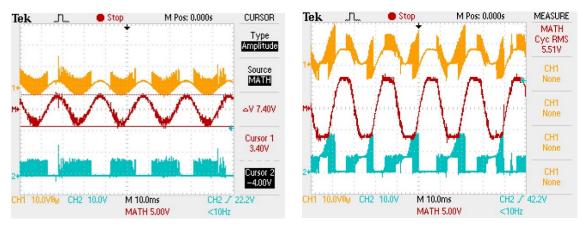

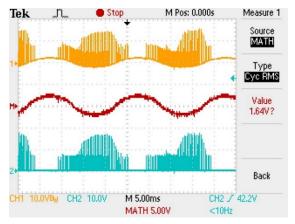

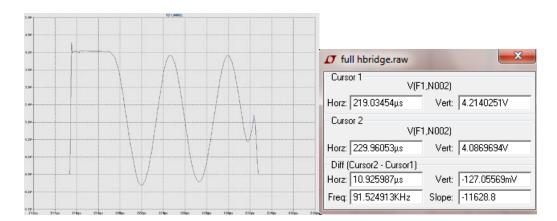

| 5.11:  | Output filtered PWM from the Arduino with 10 kHz (left) and 31250 Hz                  | 82  |

| 5.12:  | Output voltage with PWM frequency of 31.25 and 62.5 kHz                               | 82  |

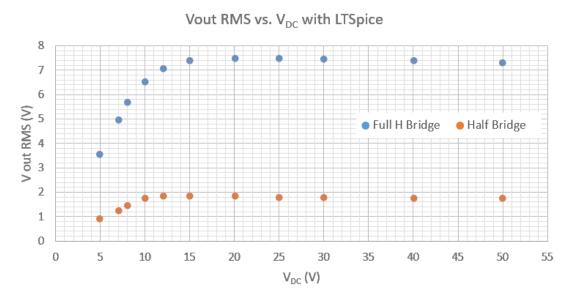

| 5.14:  | Vout (RMS) vs. V <sub>DC</sub> input voltage for a Full-H Bridge and a Half Bridge    | 84  |

| 5.15:  | V <sub>GS</sub> on a low side MOSFET                                                  | 85  |

| 5.16:  | V <sub>DS</sub> voltage on a high-side (top) and low-side MOSFET (bottom)             | 85  |

|        | Vds on high-side and low-side MOSFETS for PWM freq. of 31.25 kHz and 62.5 kHz         |     |

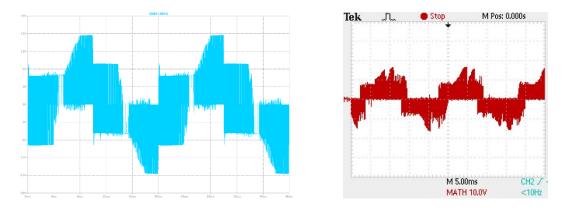

| 5.18:  | Output waveform without filter with LTSpice (left) and real (right)                   | 86  |

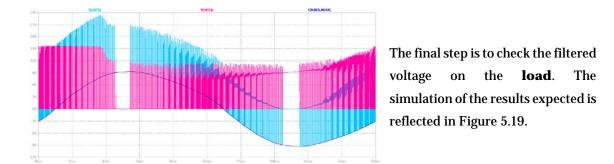

| 5.19:  | Output waveforms. Left leg (blue), right leg (pink) and difference (dark blue) in the |     |

| resist | or with 31250 Hz. Vertical axis: 3V/div                                               | 86  |

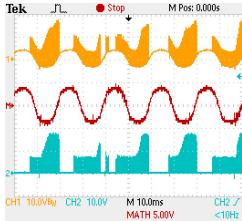

| 5.20:  | Output waveforms with 31250 Hz (left) and 62500 Hz (right)                            | 87  |

| 5.21:  | Output waveforms with 10kHz                                                           | 87  |

| 5.22:  | I <sub>D</sub> on a high side MOSFET                                                  | 88  |

| A.1:   | Unipolar PWM waveforms [2]                                                            | 100 |

| A.2:   | H-Bridge schematic                                                                    |     |

| A.3:   | Ringing drain-to-source voltage                                                       |     |

| A.4:   | Thermal resistances of IRF60B217 [Appendix B]                                         |     |

| C.1:   | Waveform Generation Mode Bit Description for Timer 0 [21]                             |     |

| C.2:   | Waveform Generation Mode Bit Description for Timer 1 [21]                             |     |

| C.3:   | Waveform Generation Mode Bit Description for Timer 2 [21]                             |     |

| D.1:   | Schematic with LTSpice software                                                       |     |

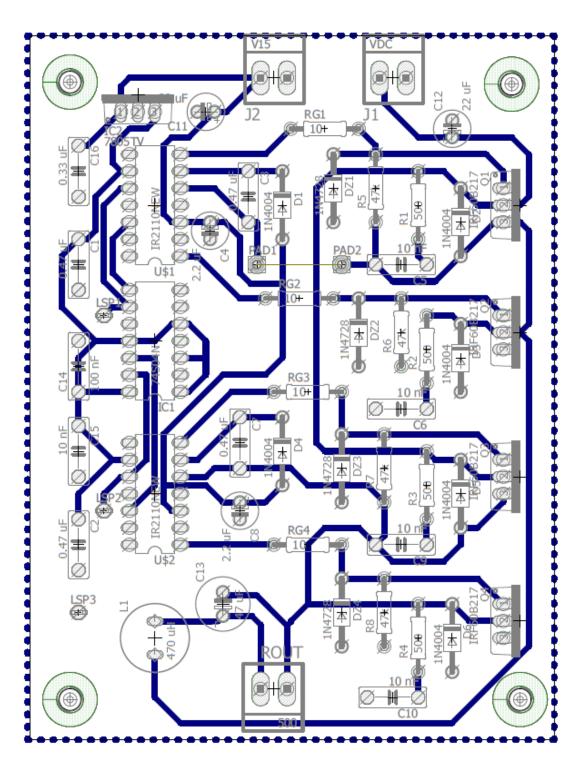

| D.2:   | Schematic with EAGLE software                                                         |     |

| D.3:   | Board design.                                                                         |     |

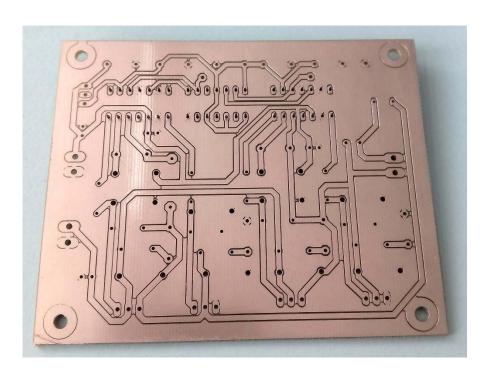

| D.4:   | Real PCB without elements. Bottom side                                                |     |

| D.5:   |                                                                                       |     |

|        |                                                                                       |     |

# List of tables

| 2.1: | Resume of states in an elementary switching cell                 | ک   |

|------|------------------------------------------------------------------|-----|

| 2.2: | Types of filters and main features.                              | 21  |

| 3.1: | Resume of features and selection [12]                            | 31  |

| 3.3: | Average losses on the semiconductors in one period               | 40  |

| 3.3: | Description and values selected for the input voltages.          | 47  |

| 4.1: | Pins, Timers and default frequency of PWM outputs on Arduino UNO | 66  |

| 5.1: | Output RMS voltage obtained for different loads.                 | 81  |

| 5.3: | Simulated losses in the MOSFETs (M) and diodes (D)               | 83  |

| B1:  | Values computed for different PWM frequencies.                   | 107 |

| D.1: | Resume of the components of the circuit                          | 112 |

# Chapter 1

# Introduction

## 1.1 Objectives

The main objective of this project is the design, simulation and testing of a single-phase inverter for educational purposes. In order to achieve this, the first step is the **analysis** of the device, with a full regard into topologies, modulation and components.

After the definition of the performance criteria, the **real elements** have to be selected. Therefore some computations will be necessary to determine the concrete parts.

The aim is to implement the **PWM modulation** digitally, and for this purpose, the possibilities provided by the microcontroller will be analysed.

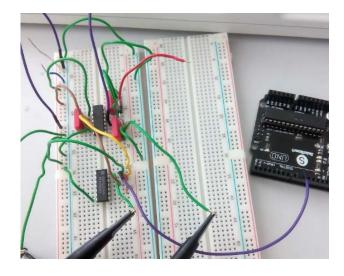

Once the **theoretical simulation** is made, the circuit should be built into a **protoboard** for real testing. As a final step, a **PCB model** of the circuit will be developed.

# **1.2 Scope**

This project follows all the steps necessary to design a real device. First of all a **theoretical approach** into inverters and their parts is made in Chapter 2 in order to have a first idea of the circuit.

Chapter 3 goes into the **design** with detail, with a complete discussion and selection of all the elements needed. Also, the requirements for the inverter are set, in order to measure its quality.

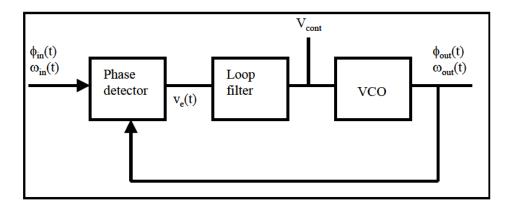

One of the key aspects is the **microcontroller**. Therefore, Chapter 4 focuses on its characteristics and explains the possibilities available regarding PWM generation.

After the theoretical development, on Chapter 5 the **results** obtained on the real circuit are collected. Also a computer software is employed to simulate them in order to have a better idea of the results expected.

Finally, Chapter 6 collects a **resume** of the objectives achieved, as well as some recommendations and guidelines for further improvements on the project.

The final **appendixes** gather a complete explanation of the calculations made, the complete code implemented and the technical documents of the work.

# Chapter 2

# Single – Phase Inverter

This chapter presents the general topic of this work: the **single phase inverter**. Not only definition, but applications and components are described in those pages.

The main **topologies** available for inverters will also be discussed, in order to justify the final decision of a Full Bridge configuration. Also, an insight into its main component, the **elementary switching cell**, is given.

Within the elementary switching cell, **semiconductors** are the devices responsible for its operation. Due to their importance, a brief description of the main types, covering structures and schematics is included. Also, a final comparison depending on frequency and power can be found.

An important block in this chapter is the **PWM modulation**. After a first definition and explanation, the two main options for modulation are described: bipolar and unipolar.

Finally, other parts of the inverter are commented, as the **driver** and the **filter**.

### 2.1 Definition

A power inverter, or inverter, is an electronic device or circuitry that changes **direct current** (DC) into **alternating current** (AC).

Depending on the number of phases of the AC output, there are several types of device. **Single-phase** and **three-phase** inverters are the most common configurations. Figure 2.1 shows a schematic of their basic performance.

Figure 2.1: Single - phase and three - phase voltage inverters [1]

### 2.2 DC - AC current

Technically, there are two ways in which electricity can be transmitted: direct current and alternating current.

**Direct Current (DC)** is the unidirectional flow of electric charge. If a constant voltage is applied across a circuit, it results in a constant current. DC can be produced by different sources, being batteries the most common ones. Also dynamos, power supplies or solar cells are examples of DC generators.

Figure 2.2: Direct and alternating current and voltage [2]

On the other hand, in **Alternating Current (AC)** the flow of electric charge periodically reverses its direction. The most usual waveform of AC is a sine wave, but it can also be triangular or square wave.

In order to transfer electrical power into different kinds of current, special devices are required. Converters AC/DC are called **rectifiers** and **inverters** are DC/AC converters. It is important to do this transformation in the most efficient way in order not to lose energy.

Another important issue to consider is **frequency**. In a DC voltage, given that the voltage value is constant, frequency is zero. However, when AC voltage is involved, it is necessary to define the number of repetitions per unit of time of a periodic event, that is to say, the frequency. **Period** is the inverse of frequency, and it can be defined as the amount of time required in order to complete a repetitive cycle.

### 2.3 Applications

When it comes to transform a source of Direct Current into an Alternating Current, the amplitude of output and input do not need to be the same. The most widespread converters are the **voltage inverters**, also called power-reducers, as the output voltage is lower than the input.

Sometimes combined with boost converters, inverters are used in a wide range of applications, as injection of energy to the grid on renewable energies, isolated generation or electric drives.

An example for this is electricity generation with solar cells. When sun light reaches a cell, electrons are released. Applying an electric field, they can be taken out and result in a DC current. In order to put this electricity on the grid, an inverter is needed. Another example is an AC device connected to a battery as power source. Given that direct connection is not possible, an inverter is required as an intermediate device.

Figure 2.3: Examples of applications [3]

### 2.4 Output: modified sine wave and pure sine

With regard to their output, two different types of power inverters can be found: modified sine wave and pure sine wave.

On **modifying sine wave** inverters, the output waveform is similar to a square but with a null period between positive and negative values. Due to its high distortion levels, it is not commonly used, as some devices do not work properly with it.

On the other hand, a **pure sine inverter** provides a sinusoidal waveform, requiring more complicated circuitry but assuring better efficiency and lower distortion than the previous type. The majority of the inverters are pure sine inverters, given that their output can be applied to all loads.

The differences between both waveforms can be appreciated in Figure 2.4. Also, a square wave is included in order to establish a reference for comparison. It can be seen that the modified sine is the intermediate waveform between the square and the sine. While modified sine rises or falls instantaneously after sitting at zero for a moment, the pure sine waveform passes through all values between minimum and maximum, resulting in a smoother input for the load.

Figure 2.4: Square, modified and sine wave [4]

### 2.5 Elementary switching cell

The main component of an inverter is the **elementary switching cell**. It connects an input and an output source and basically consists of two switchers. Regarding the sources, some basic electricity rules must be followed:

- Two current sources cannot be connected in series unless they have the same value. Otherwise charges start to be accumulated, as the principle of charge conservation is not achieved.

- Two voltage sources of different value cannot be connected in parallel. In case this happens, there is a voltage drop and a current between the sources appears. The final voltage would be equal for both sources but in no case the highest value of voltage would be achieved.

Consequently, one source must be of **current** and the other of **voltage**. Also it is necessary to take into account that a voltage source cannot be short-circuited (with an inexistent load the current would increase only limited by parasitic resistances) and that a current source cannot be left in open circuit (the charges would not flow). Thus, there are only **three possible connections** between the sources, as shown in Figure 2.5. Energy flows only on states 1 and 3.

Figure 2.5: Connection states allowed [1]

In case the current source is the input, the converter is a **step-up (boost)**. Otherwise, if the voltage source is the input, the converter works as a **step-down (buck)**.

In an elementary switching cell, the interrupters cannot be opened or closed at the same time, so they must be **complementary in performance**. Therefore, only one connection function is required for both.

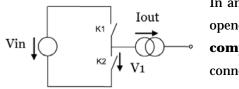

Figure 2.6: Elementary switching cell

Table 2.1 is an example of the output voltage regarding different values of the connection function. The switch  $K_1$  is connected to F and the input voltage is Vin.

| Connection function F | K1 | K2 | V1  |

|-----------------------|----|----|-----|

| 1                     | 1  | 0  | Vin |

| 0                     | 0  | 1  | 0   |

Table 2.1: Resume of states in an elementary switching cell.

### 2.6 <u>Semiconductors</u>. <u>Selection of interrupters</u>

Power semiconductors are the main part of the switching cell. The inverter's features depend largely on their performance and characteristics.

Basically, all semiconductors consist of **PN junctions**. Those are achieved doping silicon with boron (P layer) or phosphorus (N layer). When a certain voltage is applied to the junction, the internal charges move, letting the current flow through it. If the voltage is not enough, the charges do not flow and therefore the semiconductor acts like a blocker. An ideal semiconductor would perform as an **ideal switch**, being its main characteristics on- and off-control, instantaneous switching, null impedance in conducting and infinite impedance in cut-off. Also, reversibility regarding current and voltage and the voltage range in conducting are issues that define a semiconductor.

In this section, a brief insight into different semiconductors will be given.

### 2.6.1 Types of semiconductors

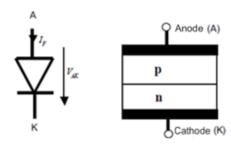

### - DIODE

A diode consist of a single PN junction. It is the simplest semiconductor and has no on- and off-control. Its symbol and structure are reflected in Figure 2.7.

Figure 2.7: Symbol and structure of a diode [1]

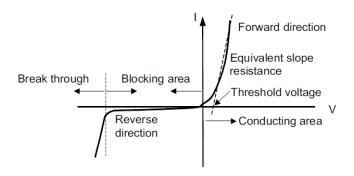

When a positive voltage over a specific value (Threshold voltage) is applied between P (anode) and N (cathode) it conducts, whereas a negative voltage results in the cut-off of the diode. However, there is a limit for negative voltage applied, as the PN junction can be broken. Figure 2.8 shows the **static characteristic** of a diode. Three main areas can be observed: forward direction (diode conducting), blocking area (diode cut) and break through (diode destroyed).

Figure 2.8: Current-voltage characteristics for a diode [5]

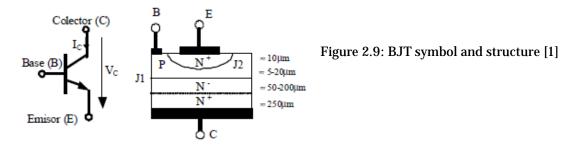

### - **BJT**

Two PN junctions result in a **Bipolar Junction Transistor** (BJT). The basis of this semiconductor is to amplify current. Applying a positive voltage between collector (C) and emitter (E) is not enough to make it conduct. Therefore, it is required to introduce a positive current on the base in order to achieve current circulation, with a base-to emitter voltage ( $V_{BE}$ ) over the threshold value.

BJTs have current gains in the order of 10 for comparatively high voltage drops. As one of their drawbacks, it is necessary to introduce high currents on the base in order to make the device work in the forward-active area (amplification of current). Also, high reverse base drive currents are required to obtain a fast turn-off. For these reasons, they are not commonly used in power electronics.

### **MOSFET**

The **Metal Oxide Semiconductor Field Effect Transistor** or MOSFET is a voltage controlled semiconductor, unlike BJT, that is current controlled.

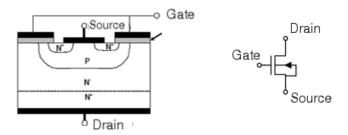

There are two types of MOSFETs: channel N and channel P, but this last one is not commonly used in power electronics. The voltage control is between gate and source, and normally must be above 10 Volts in order to switch on the semiconductor. Structure and symbol of an N-Channel MOSFET are shown in Figure 2.10.

Figure 2.10: Structure and symbol of an N-Channel MOSFET [1]

Basically, in order to turn it on, a voltage between gate and source ( $V_{GS}$ ) must be applied. This fact, together with a positive voltage between drain and source ( $V_{DS}$ ), result in an electron channel that allows a current flow in the drain ( $I_D$ ).

This semiconductor is commonly used in low voltage and low power applications, as microelectronics. Also, when a high switching frequency is required.

Regarding their static behaviour, reflected in figure 2.11, MOSFETs can operate between the breakdown voltage and the maximum direct voltage. Below and over these values, the semiconductor gets into avalanche and the junctions are destroyed. When conducting in the ohmic region, MOSFETs behave as a resistor, amplifying the current. On the other hand, in the active region the current is linear.

Figure 2.11: Static behaviour of an N-Channel MOSFET [5]

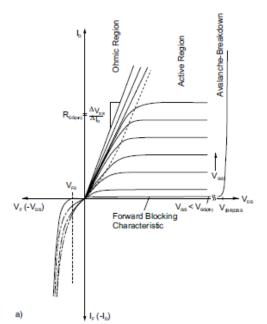

### **POWER-MOSFET**

As a concrete type of MOSFETs, Power MOSFETs are specially designed to handle higher power levels. Due to their low gate drive power, fast switching speed and good paralleling capability, they are commonly used in power electronics.

The most common structure in Power MOSFETs is the **Vertical Diffused MOS (VDMOS)**, with the source electrode over the drain, which results in a vertical current when the device is conducting. Whereas Lateral Diffused MOS (LDMOS) are mainly used in high-end audio amplifiers, VDMOS are the option normally selected for switching applications.

Figure 2.12: Cross section of a VDMOS, showing an elementary cell [27]

The internal structure of an elementary cell of a VDMOS is shown in Figure 2.12. The complete semiconductor is composed of several thousands of cells.

The source metallization connects  $N^+$  and P implantations, creating a diode between the drain (cathode) and the source (anode) of the MOSFET. This **body diode** can be employed as freewheeling diode in H-Bridge configurations.

The main difference between Power MOSFETs and normal MOSFETs is the current capacity and the gate capacitance. Whereas normal MOSFETs perform better in higher frequencies, Power MOSFETs are a better option regarding high current and voltage applications. Also, power MOSFETs have much lower resistance while conducting, minimising conducting losses.

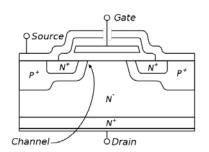

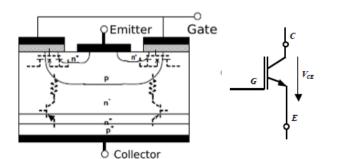

### - <u>IGBT</u>

The **Insulated Gate Bipolar Transistor** is similar to a MOSFET but with a third PN-junction. This allows controlling it with voltage, as a MOSFET, but with output characteristics similar to a BJT regarding high loads and low saturation voltage. Its schematic structure and symbol are reflected in Figure 2.13.

Figure 2.13: Structure and symbol of an IGBT [1]

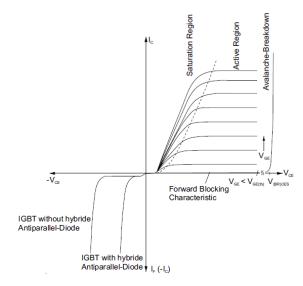

Four main regions can be observed on its **static behaviour**. From the left to the right in figure 2.14, the avalanche region is the area when a voltage below breakdown voltage is applied, resulting in the destruction of the IGBT. The **cut area** includes values from breakdown voltage up to threshold voltage. The IGBT does not conduct in this region. On the **saturation** region, the IGBT behaves as a voltage source and a series resistance. With low variations of voltage, high amplification of current can be achieved. This area is the most desirable for working. If the voltage is augmented, the IGBT enters in **active** region, and current remains constant. There is a maximum voltage applied in order the IGBT not to enter in avalanche.

Figure 2.14: Static behaviour of an IGBT [7]

It is the most used semiconductor in power electronics, given that it can support a wide range of voltage from few volts to kV and powers between kW and MW. Also, in applications with switching frequencies lower than 20 kHz, it is the semiconductor commonly selected.

### Other semiconductors

IGBTs and MOSFETs are the most used semiconductors in power electronics. However, especially in very high power, other semiconductors like THYRISTORs or GTOs are employed.

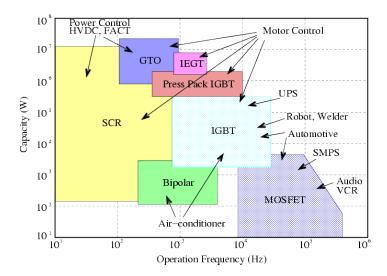

Figure 2.15: Selection of semiconductors regarding capacity and operation frequency [6]

In Figure 2.15, a selection of semiconductors depending on power and operation frequency is resumed. Regarding power, at low frequencies SCR (a type of THYRISTORs) are the most used. As frequency increases, they are replaced by GTOs or IGBTs. Finally, with high frequencies MOSFETs are the semiconductors selected, as their switching losses are lower comparing with the rest. From the graph, it is remarkable the lack of semiconductors with both high frequency and high power performance. The difficulty of combining both features is directly related to losses and heat evacuation.

### 2.6.2 Selection of semiconductors for an inverter

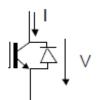

The selection of the interrupters depends on the reversibility required for the voltage and the current source. On an inverter, it is only necessary current reversibility. Hence, an interrupter of **three segments** must be chosen.

Selecting a **transistor and a diode in antiparallel**, the turning-on of the transistor can be controlled with voltage. When the voltage applied is positive and an on-order is given, the transistor conducts and the current is positive. If the voltage is negative, the diode conducts and the current is negative.

Figure 2.16: Semiconductors chosen

Whereas the diode is always in a switching cell, different **transistors** can be chosen. Criteria applied for the decision regards applications, switching frequency, velocity and voltage required. On Chapter 3, a discussion about the best semiconductor to choose will be held.

### 2.7 Inverter topologies: Half - Bridge and Full - Bridge

Regarding inverters, there are several topologies available, being the most common ones Half Bridge and Full Bridge. This section collects a brief explanation of them.

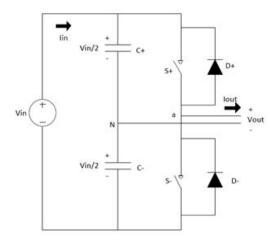

### 2.7.1 Half - Bridge

In this topology, only **two switchers are required**. The DC input is divided in two identical sources and the output is referenced to the middle point.

Figure 2.17: Single-phase Half-Bridge voltage inverter. [7]

A **capacitor divisor** is used to achieve the medium voltage point (N). By controlling the voltage in N, direct current injected in the alternate side is assured to be zero.

In addition to this, only one switching cell is required. Therefore, it is a cheap alternative and the conducting losses are not excessively high.

On the other hand, in order to obtain the same value of power, higher currents are required, as voltage is lower. In case a high voltage is needed in the output, an elevator is commonly used as first step, as the input voltage must be double than the output desired. Regarding switching losses, the semiconductors must be designed for 2Vout. This fact makes this topology the **worst in performance**, as switching losses become excessively high.

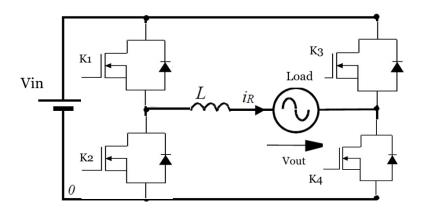

### 2.7.2 <u>Full H-Bridge</u>

In a Full H-Bridge, the alternate output voltage (Vab in Figure 2.18) is obtained by the difference between two branches of switching cells. Therefore, **four switchers** are needed. To maximize the fundamental component of the output voltage, the fundamental component of the voltage on each branch (Vao and Vbo) must be 180° out of phase. The semiconductors of each branch are complementary in performance, which is to say when one is conducting the other is cut-off and vice versa. This topology is the most widely used for inverters.

The semiconductors must be designed only for Vout, but as a disadvantage, four switchers are required and therefore, losses can become elevate.

Vin/2 - C+ S1+ D1+ S2+ D2+ Vout

Vin/2 - C- S1- D1- S2- D2-

Figure 2.18: Single-phase Full H-Bridge voltage inverter [7]

### 2.8 PWM Modulation

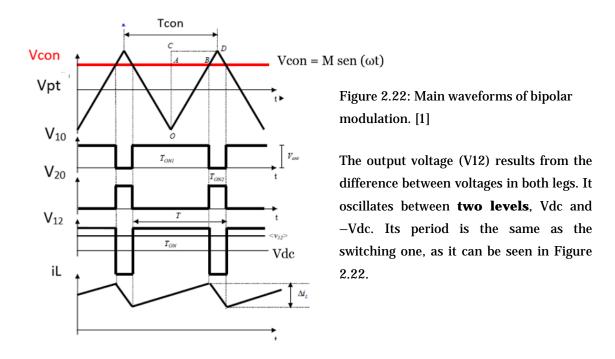

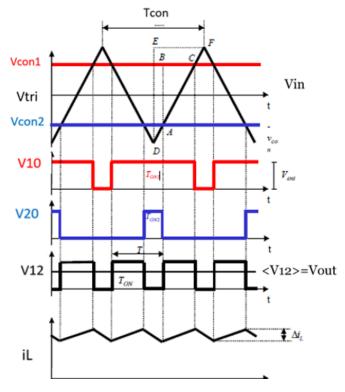

In order to obtain the connection function for the semiconductors, a modulation technique called PWM is employed. The basics of **Pulse Width Modulation** (PWM) is the variation of the duty cycle of a periodic signal. The duty cycle (D) is defined as the variation of the positive part of the signal ( $T_{on}$ ) related to the period (T).

$$D = \frac{T_{on}}{T}$$

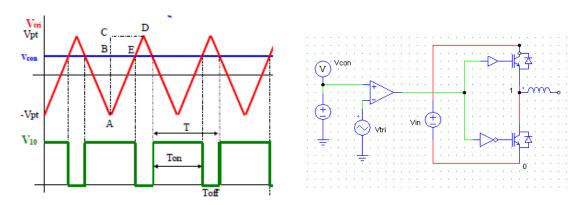

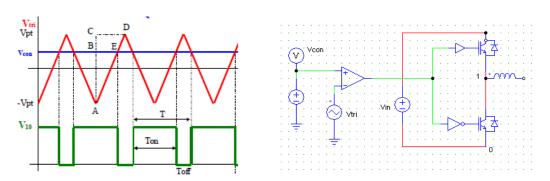

**In analog circuitry**, a PWM is obtained comparing a signal control ( $V_{con}$ ) with a triangular wave. For this purpose, normally a comparator is used. Thus, the output will be 1 if the positive leg of the comparator is higher than the negative one and 0 if it is lower. Figure 2.19 reflects schematic and waveforms obtained in an analogical PWM circuit.

Figure 2.19: PWM waveforms and schematic.

It must be pointed out that with constant Vcon only a fixed duty cycle can be obtained. For the purpose of having a **varying duty cycle**, the signal control must be **sinusoidal**. This way, as Vcon is not constant, the positive part relating to the period changes. Hence, two frequencies must be considered. Vcon oscillates normally at the **output desired frequency**, which is usually a low value, 50 or 60 Hz. Also, it is necessary to determine the frequency of the triangular wave. This frequency is directly related to the **switching frequency** of the semiconductors, and must be carefully chosen. Normally, the value selected is over 20 kHz, in order to overcome the human hearing threshold.

Basically, there are two main techniques to obtain a PWM: bipolar and unipolar modulation. Both can be applied to a Full H-Bridge, and will be studied in the following section. The high-side interrupters are named K1 and K3 and the low-side are K2 and K4.

### 2.8.1 <u>Bipolar Modulation.</u>

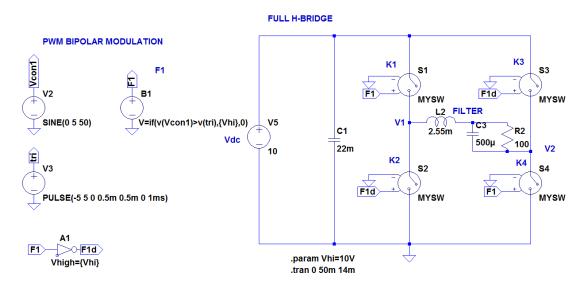

In bipolar modulation, the output voltage oscillates between two values (Vdc and –Vdc in Figure 2.20), hence its name.

A basic schematic of a Full H-Bridge with bipolar modulation is collected in Figure 2.20. It can be seen how in this modulation, the connection function is the same for K1 and K4 and for K2 and K3. This means, only **one signal control is required**. As the switchers are complementary in performance on each branch, the connection function must be inverted in order to achieve this.

Figure 2.20: Analogic circuitry for bipolar modulation in LTSpice software

The connection function, and therefore the switching of the MOSFETs depend on the difference between the control voltage (Vcon) and the triangular wave (Vtr). The following schematic resumes the performance of bipolar modulation.

Figure 2.21: Resume of bipolar modulation.

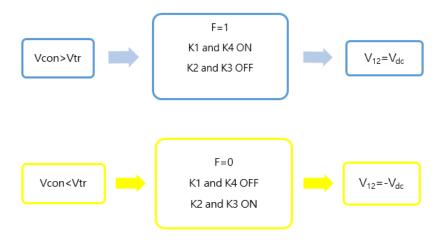

Also, the main waveforms are collected in Figure 2.22: Vcon (sinusoidal control voltage), Vpt (triangular voltage) V10 and V20 (voltage on the low side switchers of each branch), V12 (output voltage without filtering) and iL (current on the inductance).

In bipolar modulation, the output voltage **switching harmonics** are the sum of the switching harmonics of both branches. In order to reduce them, an option is increasing switching frequency, as this eases the filtering. However, as a result the switching losses may become too large.

An important advantage of this modulation is the **constant voltage to ground** (common mode voltage), which make bipolar modulation the one preferred in applications as photovoltaic systems without transformer.

### 2.8.2 <u>Unipolar Modulation.</u>

Unlike bipolar modulation, in case unipolar modulation is implemented in a circuit, the connection function is **different in both branches**. Given that the switchers must be complementary in performance, both branches of the bridge are related by the triangular voltage. Furthermore, the sinusoidal control voltage is opposite in sign in both legs.

$$V_{con1} = -V_{con2}$$

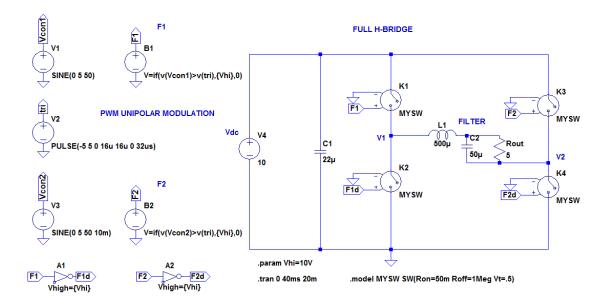

Figure 2.23 shows a simple schematic of the implementation of unipolar modulation with LTSpice software.

Figure 2.23: Analogic circuitry for unipolar modulation in LTSpice software.

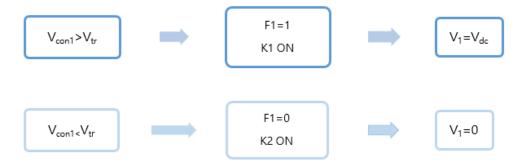

The operation of the connection functions is the same as in bipolar, but instead of having two levels of voltage in the output, there are **three**: Vdc, 0 and –Vdc. This way, the output is **more accurate** than in bipolar modulation. A resume of the performance of unipolar modulation is collected below (Figure 2.24). Also, the main waveforms can be observed in Figure 2.25.

Figure 2.24: Resume of unipolar modulation.

The period of the output voltage is half the switching one and therefore the **output frequency** doubles the switching one. As the **harmonics** are in a higher frequency, for the same switching frequency the output inductance can be smaller than in bipolar modulation.

Also regarding harmonics, as the output voltage results from the difference between branches, the even families of harmonics have double amplitude, given that they are 180° out of phase on each branch. On the other hand, the odd families are in phase and do not appear in the output.

Figure 2.25: Main waveforms of unipolar modulation [1]

Unlike bipolar modulation, unipolar modulation has only one sign on each semiperiod, hence its name. The comparison between both modulations and their outputs is reflected in Figure 2.26. It can be appreciated how the filtered waveform (sinusoidal) is clearer with unipolar modulation. Also the difference between output levels (two in unipolar and three in bipolar) can be seen.

Figure 2.26: Output waveform with bipolar modulation (up) and unipolar modulation.

### 2.9 Driver

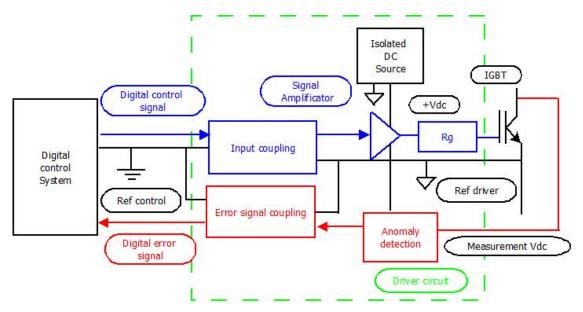

A driver is a device which adapts the connection function to the requirements of the semiconductors. As the connection function only oscillates between two values, sometimes it is necessary to modify the signal in order not to damage the semiconductors.

### **Main functions:**

- Amplification of the control signal in order to adapt it to the desired levels of voltage and current.

- Galvanic isolation: to avoid electrical contact between two parts of the circuit.

- Protection against low feeding voltages or current that could damage the semiconductors.

Figure 2.27: Functional schematic of a driver [1]

## 2.10 Filter

The output voltage is the difference between voltages in the two branches of the bridge. Its waveform is **squared** and therefore a filter is required in order to obtain a sine. Also, it contains a large number of harmonics, which may disturb the correct operation of the output load connected.

A filter is basically a circuit which modifies frequency components between its input and output. It can be analogic or digital and depending on its behaviour, there are mainly four types.

| Type of filter | Features                                                              |

|----------------|-----------------------------------------------------------------------|

| Low pass       | They let pass low frequencies and attenuate the ones over a cut point |

| High pass      | They attenuate frequencies below a cut point                          |

| Band pass      | They let pass frequencies between a range                             |

| Band rejection | They block frequencies between a range                                |

Table 2.2: Types of filters and main features.

Once the type of circuit is selected, the cut point and the ranges of frequencies can be chosen by modifying the components.

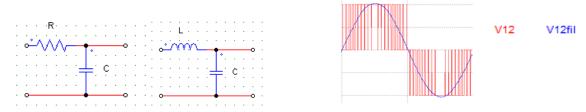

As in this case the objective is to **attenuate harmonics**, a **low pass filter** will be selected. For a low pass filter, there are two options regarding circuitry: RC (resistor – capacitance) or LC (inductance – capacitance).

Figure 2.28: RC and LC low pass filters and waveforms.

In Figure 2.28 the output waveform of an inverter before and after an LC filter can be observed. To select the components, it is necessary to determine maximum ripple current, ripple voltage and cut frequency.

## 2.11 Other projects

Having a look into previous researches on this topic, several options can be found. Between **low voltage single-phase inverter** designs, an important block of projects focus on the generation of analogical PWM. This is the example of "*DC/AC Pure sine wave inverter*" (J. Doucet, D. Eggleston, J. Shaw. Worcester Polytechnic Institute, ref [4]), which provides a detailed description of the analogical PWM generation. On higher voltages, there are various examples of design of inverters, as "*Sistema fotovoltaico aislado: inversor monofásico"* (Barnetxea, A., ref [8]) or "*Diseño e implementación experimental de un inversor monofásico operando en modo isla"* (Martín, R., ref [10]).

All of them have in common that the **PWM generation is analogical** and therefore describe it with detail. On the other hand, this project is focused on the **digital implementation**, also with regard to further control developed on the circuit.

## Chapter 3

## Design

The aim of this chapter is to gather all the design aspects on an inverter. First of all it is necessary to make an approach to the specific **features** of the problem. Also, a detailed description of the **design criteria** is developed, that is to say, which aspects are the most important regarding the quality of the inverter.

In these pages, a discussion and explanation about different decisions taken in designing is given. After selecting the **topology** of the inverter and its **components**, it comes to compute the different elements of the circuit, as the DC bus capacitor, the output inductance, or the filter. Then, a description of the **losses** in the different semiconductors is made and employing the software LTSpice they are also estimated.

A key aspect in the design is the value of the **switching frequency**. The possibilities available, as well as a discussion about **PWM modulation** are also reflected.

The chapter ends with the **circuit protections**. Not only a description, but also a selection of the components necessary for the adequate operation of the device is made.

## 3.1 <u>Context (features of the problem)</u>

This project is focused on the design of a voltage inverter for **educational purpose**. Therefore, the power and voltage required are not excessively high. A rough estimate would be between 30 and 50 Watts as maximum power and a voltage range between 5 and 15 volts.

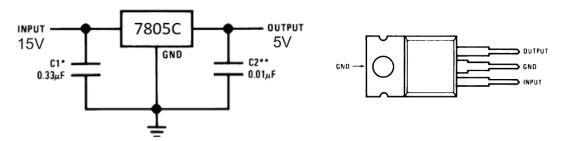

In this context, it can be established a relationship between input and output voltage, as the DC voltage must be  $\sqrt{2}$  times the maximum AC voltage. Considering 15 volts as input voltage, the output would be **10.6 effective** volts as maximum.

Regarding frequency, the desired output sine would be of **50 Hz**, standard value in most part of the world.

Also, it is necessary to define a **switching frequency** for the semiconductors. Given that in this work an Arduino will provide the PWM signal, the frequency can be modified as desired. The best results can be achieved on a range from **35 to 62.5 kHz**, fact which will be lately explained.

Therefore, a resume of the **main features** for the inverter is:

Maximum power: 30 – 50 Watts.

Input voltage: 15 V (DC).

Output voltage: 10.6 V (AC).

Sine frequency: **50 Hz.**

Recommended switching frequency: 35-62.5 kHz.

### 3.2 Performance criteria.

A very important aspect in every design is the determination of the performance criteria, that is to say, which aspects are considered the most important regarding the results obtained.

#### 3.1.1 Efficiency

As it was mentioned in the previous chapter, energy conversion should ensure the optimal utilisation. This requirement can be determined by measuring the efficiency of the system. **Efficiency**  $(\eta)$  is defined as the relation between output and input power, usually measured in percentage. Good efficiency ratios are above 80 or 90%.

$$\eta = \frac{P_{out}}{P_{in}} . 100 (\%)$$

Directly related to efficiency are **power losses**. In semiconductors, losses appear not only while switching but also when conducting due to their internal structure. A deeper insight into losses will be given further in these pages.

A 100% successful conversion is not possible in reality. Although the efficiency rates are usually high, there is always a part of power that dissipates in the form of **heat**. Unluckily, this heat cannot be tapped. Also, it has negative effects on the device, especially regarding performance, as temperature increases and components may not work properly for this reason.

#### 3.1.2 Quality of the waveform

Not only the amount of energy obtained after conversion is important, but also its **quality**. On a pure sine inverter, the waveform should be as clear and pure as possible. There are several factors affecting this waveform, being the performance of the circuitry components an example of that, but mainly the distortion of the sine is due to **harmonics**.

Every periodical signal can be decomposed into a sum of sinusoidal functions, by means of Fourier series expansion. Therefore, the mathematical expression for a periodic voltage is:

$$v(t) = V_{DC} + \sum_{n=1}^{\infty} \sqrt{2} V_n \sin(n\omega t + \theta_n)$$

As desired component, the **fundamental component** is the one that oscillates at 50 Hz. It is the first term of the series, and the rest of components are regarded as undesired for several reasons.

$V_{DC}$  is the **DC component** of the voltage. It is the medium value of the signal and normally, this project included, is wished to be zero. In order to achieve this, different techniques can be applied. In the current design, this part of the voltage is removed as a result of the modulation used in the H-Bridge.

**Harmonics** are components whose frequency is a multiple of 50 Hz. They distort the waveform and their value decreases as the series index increases. Other problems related to harmonics are noise, possible damage in electronic circuits or overcharge of capacitances.

Not all the undesired components have frequencies multiple of 50 Hz. **Inter-harmonics** are named sub-harmonics when they appear below 50 Hz, but can also be found as a broadband spectrum.

The most common way of measuring the quality of waveform is the **Total Harmonic Distortion (THD).** It is defined as the ratio between the sum of power of all harmonic components and the power of the fundamental frequency.

$$THD = \frac{\sqrt{\sum_{n=2}^{40} V_n^2}}{V_1}$$

A good voltage THD should be ensured in order to achieve good performance. For low voltage levels, THD should be around 8%, according to UNE-EN 50160 (official standard in Spain that defines features in voltage provided to consumers by electricity distribution grids). However, it is mostly recommended to deal with no more than 5% harmonic voltage distortion factor. The largest single harmonic should not be above **3%** of the fundamental voltage [11]. A high THD can result in malfunction of the equipment.

#### 3.1.3 Reactive Power.

Regarding power, it is necessary to make a first distinction between DC and AC circuits.

On a **DC voltage circuit**, it is only necessary to take into account the power that is transformed into work or heat, called **Active Power** (P). It can be computed as the product of instantaneous voltage (V) and current (I), and its units are Watts. As they are always in phase, power can be calculated as:

$$P = V . I$$

However, dealing with **AC voltage circuits**, there are more circumstances to be considered. In this kind of circuits, apart from Active Power, there is another one which deals with the formation of electric and magnetic fields in the components of the circuit. This power is not really consumed, but fluctuates between those components and the energy source. Its name is **Reactive Power**, and it is represented with letter Q. Its units are volt-ampere reactive (Var).

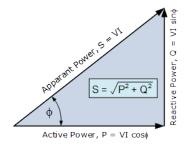

The way of relating those two powers is **Apparent Power** (S), which is the vector sum of both Active and Reactive Power. It is measured in Volt-Amperes (VA).

Figure 3.1: Relation between Active, Reactive and Apparent Power [17]

The existence of Reactive Power in an AC circuit depends on the load. If it is purely **resistive**, both current and voltage reverse polarity at the same time, and therefore their product is only positive or zero. They are said to be in phase, and the energy flow goes only in one direction. As a result, only active power is transmitted between the source and the load.

On the other hand, in case the load is **reactive**, voltage and current are out of phase. On each cycle, their product can be positive or negative, and consequently, the energy flow oscillates between the source and the load. This means, an amount of energy is not transmitted to the load (the reactive power). Depending on the gap between current and load, the quantity of energy transmitted varies. This magnitude can be measured by the **power factor (PF)**, which relates active and apparent power.

$$PF = \frac{active\ power\ (P)}{apparent\ power\ (S)} \tag{1}$$

Equation (1) can also be expressed in terms of the **phase angle**  $\vartheta$  between powers. As it is reflected in Figure 3.1, active and apparent power can be computed taking into account this angle.

$$P = V . I . \cos \vartheta$$

$S = V . I$

Therefore, equation 1 results in

$$PF = \frac{active\ power\ (P)}{apparent\ power\ (S)} = \frac{V.I.\cos\vartheta}{V.I} = \cos\vartheta$$

The maximum value for the power factor is 1, that is to say all the energy involved between the source and the load is transmitted. A bad power factor results in wastage of the exchange.

In order to transmit the same active power, in a circuit with low PF, higher currents are needed, resulting in greater losses, wires and equipment required.

The aim of this project is to design a device which could produce as high FP as possible. Sometimes it is not likely to get a good ratio of active power only with normal operation of the device. For this reason, **reactive power is often compensated**. In some cases, an external device or component, such as a capacitance, is added in order to contribute with reactive power to the consumption of the load. This solution is not very precise, and therefore, for optimal compensation, a closed loop control of current is usually employed. Controlling the diphase between current and voltage in the output it is possible to get FP closed to 1.

## 3.3 Inverter topology

Once the main features of the problem are established, the first issue to consider on the designing is the topology of the inverter. Normally, inverters deal with high voltages and a boost step is required. DC/DC before inversion or AC/AC after it are usual solutions added to the inversion step.

However, the solution adopted in this project will be that of only the **DC/AC conversion**, as the desired voltage levels can be achieved. In case a higher voltage is required, an external boost can be added.

Regarding the bridge topology, a **Full H-Bridge** will be used. This configuration requires two branches and 4 interrupters. As explained in the previous chapter, each elementary switching cell contains a transistor and a diode.

The topology selected (Figure 3.2) implies benefits in regard to Half- Bridge as lower voltages in the semiconductors and lower input voltage for the same output. Switching losses are higher in a Half-Bridge, as semiconductors deal with 2Vdc.

Figure 3.2: Full H-Bridge schematic with LTSpice software.

## 3.4 PWM Modulation. Switching frequency

A key decision in the design of an inverter is the value of the switching frequency. In the following pages, an analysis of the options will be developed. Also it is necessary to select the modulation to apply in the bridge, as the configuration and the calculation of elements vary.

#### 3.4.1 PWM Modulation

In the previous chapter, an insight into different options for PWM modulation was given. The most common ones are **unipolar** and **bipolar** modulation. In this section, a comparison between them will be made and the most suitable option for this project will be selected.

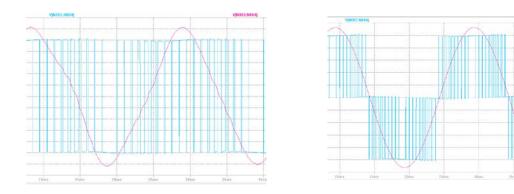

As a starting point for comparison, in both cases **the output voltage** is measured (Figure 3.3), obtaining different values and frequencies. Establishing the same switching frequency for both modulations, in bipolar modulation the **output frequency** remains the same, while in unipolar modulation it **doubles** the initial value. This allows reducing the size of passive components as inductances and capacitors but leads to higher losses. Regarding the **output values**, on bipolar modulation, they oscillate between two values, Vin and –Vin (being Vin the DC input voltage), whereas that on unipolar the output are three levelled (Vin, 0, -Vin). The higher the number of levels for modulation, the better is the waveform.

Figure 3.3: Output waveform with bipolar (left) and unipolar (right) modulation.

Regarding **harmonics**, some important points should be stressed. In **bipolar** modulation the output voltage harmonics appear at the frequency of commutation and have twice the amplitude of the branch voltage harmonics. However, in **unipolar** modulation, their frequency is twice the switching frequency and their amplitude is the same as in the branch voltage harmonics. The harmonics of the odd families do not appear in the output, as in every branch they are in phase. As the higher harmonics (first family) are odd and the frequency of the rest is higher than in bipolar, they are easier to filter. This has a direct impact on the **filtering inductance**, resulting it four times lower in unipolar than in bipolar. Another way of reducing harmonics is elevating

the switching frequency, and therefore easing their filtering. However, with this solution the losses can become really high.

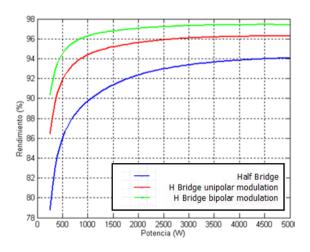

Taking into account the criteria described at the beginning of this chapter, the **efficiency** achieved with each modulation should also be analysed. Setting the **same output frequency**, on bipolar modulation the switching frequency is two times higher than in unipolar. For this reason, the switching losses are higher. An insight into Figure 3.4 lets see the different efficiencies between unipolar and bipolar modulation regarding power and with a switching frequency of 20 kHz. The maximum rates are achieved with a unipolar modulated H-Bridge, whereas the Half-Bridge configuration gets the worst results.

Figure 3.4: Efficiency for f=20 kHz vs. Power [1]

In applications such as photovoltaic systems, it is necessary to consider the differences regarding **common mode voltages**, but for the current design they will not be a decisive fact for decision.

After the discussion developed it is decided to implement **unipolar modulation**. **Efficiency** is the key feature for this decision. Also the ease to filter harmonics and the possibility to have twice the switching frequency in the output are pros that influence on the selection. As the circuit is made for educational purposes, the **size** of the components is wished to be as small as possible, and the output inductance can be reduced with this modulation.

#### 3.4.2 **Switching frequency.**

One of the most important aspects in the design of an inverter is the selection of the switching frequency, as **losses** and the **quality of the waveform** are directly related to its value. As in this case the generation of the PWM is digital, the switching frequency will be set by the **microcontroller**. A complete discussion of the possibilities will be developed in Chapter 4. Also different options will be tested on the real circuit, being the results collected in Chapter 5.

## 3.5 Selection of semiconductors

Taking into account the information given in Chapter 2 about semiconductors, in this section a further comparison between some of them will be given, in order to explain the design decision.

The first semiconductor commonly used in power electronics was **BJT**. Its simple structure and capacity to amplify current are two of its main strong points. However, in order to be turned on, high base current are needed. Also, its turn-off is relatively slow and it is highly susceptible to thermal runaway, due to its negative temperature coefficient.

When **MOSFETs** where developed, they became a good substitute for BJTs. As they are controlled by voltage, the problem with high base current is solved. Also, their temperature coefficient is positive, preventing thermal runaway. They are quick switching devices, and on their turn-off there is almost any current tail. This effect is a consequence of the remaining charges on the PN junction, and affects negatively the turning off of the switcher, delaying it and augmenting losses as a result. Structurally, MOSFETs have a body-drain diode, which can be used as free-wheeling diode for inductive loads. On the other hand, their switching losses are quite noticeable and they cannot deal with very high voltages.

**IGBTs** combine features from BJTs and MOSFETs. They are controlled by voltage but the output switching and conduction characteristics are those of BJTs. The turn-off is similar to the MOSFET one, but with a larger current tail. This fact makes their shutdown time and losses higher. Other disadvantages are the negative temperature coefficient and the lack of body-drain diodes. However, some solutions can be adopted in order to attenuate those drawbacks, as adding ultrafast recovery diode co-packed to faster the turn off. Furthermore, actual process technology and device structure have been improved, resulting in better switching characteristics [7].

The selection between MOSFET and IGBT depends on the **application**. Solutions are not unique and the features and requirements given in each application determine the choice. However, as a rough view, in Table 3.1, it can be seen a resume of some remarkable features and values.

| Feature    | MOSFET     | IGBT      |

|------------|------------|-----------|

| Voltage    | < 250 V    | >1000V    |

| Frequency  | > 100 kHz  | < 20 kHz  |

| Power      | < 3 kW     | > 3 kW    |

| Efficiency | Light load | Full load |

| dV/dt      | Limited    | High      |

Table 3.1: Resume of features and selection [12]

#### **Design decision**

In this current project, **voltage** is the key feature for deciding. As the requirements for the application are very low, the saturation voltage of the IGBTs is a handicap. Glancing over different catalogues and vendors, it is hard to get an IGBT with  $V_{CE(SAT)}$  lower than 1.4 volts. As normally two IGBTs conduct at the same time, this results in nearly 3 volts lost between input and output. This is circa a fifth of the DC voltage source so it cannot be taken as adequate. Considering MOSFETs, their behaviour at conducting can be modelled as a resistor with a value in the range of milliohms. Therefore, the difference between input and output is not so remarkable. About **frequency**, although MOSFET are commonly selected in high frequency applications, they can also deal with low values.

At the time of simulating, it is possible to compare the output waveform with ideal switchers, MOSFET and IGBTs in the following circuit:

Figure 3.5: Schematic of Full H-Bridge applied for comparison between semiconductors.

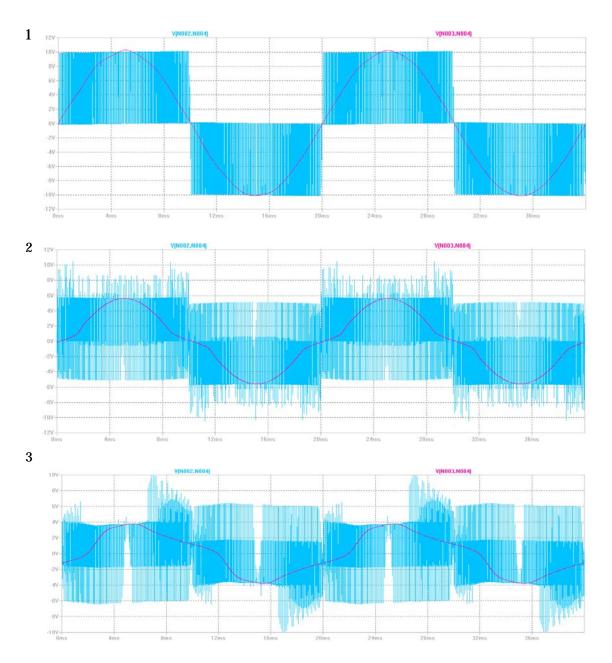

For all the cases the input DC voltage is 10V and the switching frequency is set in **10 kHz.** Figure 3.6 shows the different results obtained. The vertical axis division is 2 Volts. The blue waveform corresponds to the output voltage without filtering, whereas the pink one is the voltage in the load.

As it can be seen, while IGBT-bridge remains under 6 volts, MOSFET-bridge is closer to 10 volts. Also, the clarity of the switched waveform is notable in case of MOSFETs, and the unipolar modulation can be well distinguished. On the other hand, with IGBTs the waveform is not so clean and the peaks are more irregular.

Figure 3.6: Output voltage waveform on ideal switchers (1), MOSFET (2) and IGBT (3).

After the previous discussion, it is finally decided to select **MOSFET** as semiconductors. This way, in order to achieve a three segment switcher, a **MOSFET** and a diode in antiparallel will be chosen.

Regarding MOSFETs configuration, it is possible to find N-Channel and P-Channel semiconductors. As explained before, in power electronics the most widespread type are N-Channel MOSFETs, which have P doped silicon as substrate. When they are turned on, the conducting channel is formed by the movement of electrons. The consequence of employing this type of FETs is that a bootstrap circuit is required to drive the high-side MOSFETs' gates of the bridge.

After consulting different options and vendors available, the MOSFET selected is **IRF60B217**, from Infineon, specially designed for low voltage applications. Its complete features are collected on its datasheet [17]. The package selected is **TO-220AB**, in order to adapt easily to the breadboard and the PCB.

Figure 3.7: IRF60B217 with TO-220AB package

About the **diode**, the specific semiconductor is **1N4001**, a commonly used model, which can be provided by several vendors.

## 3.6 Dead – times on the semiconductors

Ideally, commutations in the semiconductors are instantaneous. That is to say, when the on order is given to the MOSFET, it turns on immediately. This behaviour allows the two semiconductors on each branch to be complementary in performance, avoiding their overlap.

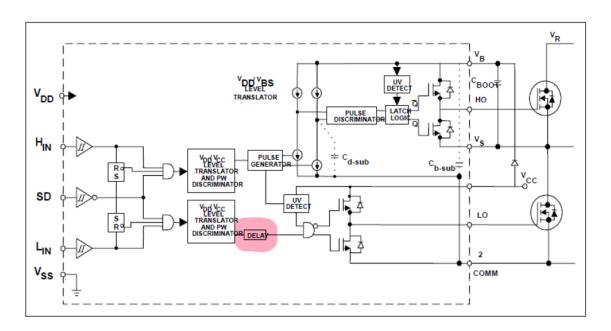

However, when it comes to reality, the MOSFET turns off a bit later than receiving the order. This time is called **turn-off delay time** ( $td_{off}$ ). The same case occurs at the time of turning on, resulting in a **turn-on delay time on** ( $td_{on}$ ). This behaviour is shown in Figure 3.9 of this chapter, being the delay times from  $t_0$  to  $t_1$ . Considering the branch as a whole, it would not be a problem in case the  $td_{off}$  and the  $td_{on}$  of the semiconductors would be equal. Unluckily, in nearly all the semiconductors the turn-off delay time is higher as the turn-on delay time.

As a consequence of this, both switchers conduct during a short period of time, which results in a transient **short-circuit**. Voltage drops and there is a peak of current tending to infinite. Depending on the delay, the value of the current could not reach very high values, as normally the overlapping lasts nano or microseconds.

In order to avoid the short circuits, a fixed delay is introduced on the signal of the semiconductor that will be turned-on. This delay is called **dead time**, and during it the voltage of the branch depends on the current sign. As a result, there is an error in the voltage.

Figure 3.8: Error due to dead time in semiconductors [1]

Figure 3.8 shows the performance of the voltage gate-source ( $V_{GS}$ ) in both semiconductors of a branch. It can be seen that when the connection function changes its value to high, there is a delay between the switching of both semiconductors (Tm). As a result, an error on the voltage appears ( $\epsilon$ ).

Nowadays, breakthroughs in power electronics let work with very low turn-off delays. As an example, on the MOSFET selected for this project (IRF60B217), the values for  $td_{on}$  and  $td_{off}$  are 8.3 and 24 ns respectively.

Also, the **driver** itself helps to handle with this problem. As shown in Figure 3.9, an internal delay is added on the structure of the IR2110 in order to avoid the simultaneous conduction of the switchers.

Figure 3.9: Block diagram of the IR2110 [18]

## **Losses in semiconductors**

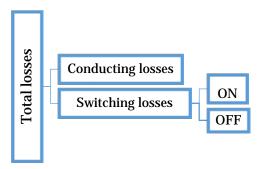

An important issue to consider in the design of the inverter are losses in semiconductors. During their performance, semiconductors cause losses not only when switching, but also while conducting. Therefore, an analysis of their internal structure and behaviour should be made in order to compute losses. After this first analysis, in this section an estimation of losses is made. Those computations are required in order to discuss the necessity of a sink.

#### 3.7.1 Analysis

In this current project, the semiconductors selected are MOSFETs and diodes. During their performance, they produce losses that become heat and result in a waste of energy converted. A complete analysis of losses include conducting losses, turn on and turn off losses.

#### **Losses in the MOSFET**

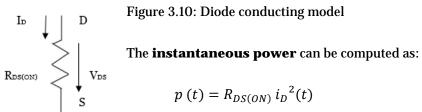

When **conducting**, a MOSFET can be modelled as a resistor with value  $R_{DS(ON)}$ . This resistor normally is of a very low value, in the range of milliohms.

Figure 3.10: Diode conducting model

$$p(t) = R_{DS(ON)} i_D^2(t)$$

Being  $i_D$  the current on the drain. In case  $i_D$  is constant, the calculations become easier. This way, the average power is:

$$P = \frac{1}{T_{ON}} \int_0^{T_{ON(MOSFET)}} R_{DS(ON)} I_D^2 dt = R_{DS(ON)} I_D^2 \frac{T_{ON(MOSFET)}}{T_{switch}}$$

This expression reflects the computation of the average power only when the MOSFET conducts. For this reason, the duty cycle appears on it. Its value depends mostly on the drain current  $I_D$ , as it appears squared.

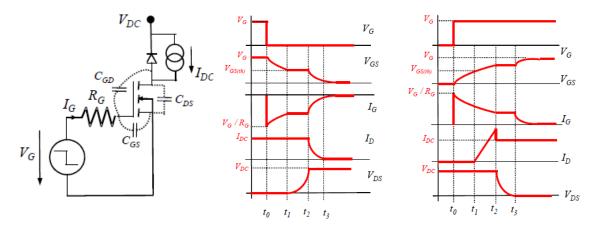

Regarding **switching losses**, the turning-on and off of the MOSFET should be taken into account, as in both cases voltages and currents appear at the same time, resulting into losses. In figure 3.11, the model of the MOSFET and the variations of current and voltage are shown.

Figure 3.11: Model and waveforms of turning on (left) and off of the MOSFET [1]

Switching losses appear in both cases between t1 and t3. As the switching is not instantaneous, current and voltage deal together during those moments, resulting in losses.

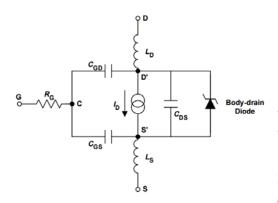

In order to turn-on and off the MOSFET, the electrons of the different layers in which load circulates must be introduced and removed. This behavior can be modelled as **parasitic capacitances.**  $C_{iss}$  is the input capacitance, and models the introduction of electrons.  $C_{oss}$  is the output capacitance, and takes into account the removal of electrons. Finally,  $C_{rss}$  is the Miller capacitance, and reflects the Miller effect (the increase in the equivalent input capacitance of an inverting voltage amplifier as a result of the increase of the effect of capacitance between the input and output terminals). The lower Vds, the higher are these capacitances.

Figure 3.12: Capacitances on a MOSFET [1]

Figure 3.12 shows the schematic and composition of the capacitances that can be found on a MOSFET. At the time of computing the losses, the energy involved depends on the drain-source voltage ( $V_{DS}$ ), the drain current ( $I_D$ ), the control voltage ( $V_G$ ), and the gate resistor ( $R_G$ ).

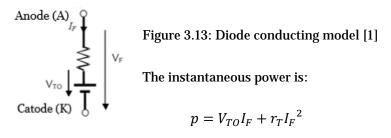

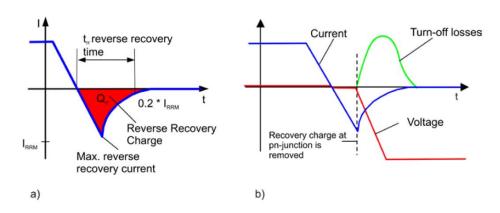

#### Losses in the diode