# Silicon-Based 0.45-0.47 THz Series-Fed Double Dielectric Resonator On-Chip Antenna Array Based on Metamaterial Properties for Integrated-Circuits

## Mohammad Alibakhshikenari<sup>1\*</sup>, Bal S. Virdee<sup>2</sup>, Chan H. See<sup>3,4</sup>, Raed Abd-Alhameed<sup>5,6</sup>, and Ernesto Limiti<sup>1</sup>

- Electronic Engineering Department, University of Rome "Tor Vergata", Via del Politecnico 1, 00133, Rome, ITALY

London Metropolitan University, Center for Communications Technology & Mathematics, School of Computing & Digital Media, London N7 8DB, UK

- <sup>3</sup> School of Eng. and the Built Environment, Edinburgh Napier University, 10 Colinton Road, Edinburgh, EH10 5DT, UK

<sup>4</sup> School of Engineering, University of Bolton, Deane Road, Bolton, BL3 5AB, UK

- <sup>5</sup> School of Electrical Engineering & Computer Science, University of Bradford, BD7 1DP, UK

<sup>6</sup> Depart. of Communication and Informatics Eng., Basra University College of Science and Technology, Basra 61004, Iraq

\*alibakhshikenari@ing.uniroma2.it

Abstract –The antenna array designed to operate over 0.45-0.47 Terahertz comprises two dielectric resonators (DRs) that are stacked vertically on top of each other and placed on the surface of the slot antenna fabricated on a silicon substrate using standard CMOS technology. The slot created in the silicon substrate is meandering and is surrounded by metallic via-wall to prevent energy dissipation. The antenna has a maximum gain of 4.5dBi and radiation efficiency of 45.7% at 0.4625 GHz. The combination of slot and vias transform the antenna to a metamaterial structure that provides a relatively small antenna footprint.

Keyterms—CMOS, dielectric resonator antenna (DRA), millimeter wave, terahertz, on-chip antenna, silicon.

#### I. INTRODUCTION

Wireless system-on-chip (SOC) applications are becoming prevalent with the advancement of low-cost silicon technology [1]-[3]. To eliminate the need for external off-chip antenna connections and the associated package processing the interest in implementing on-chip antennas have become of great interest. The consequence of on-chip antenna is to circumvent gain loss and overall size increase [4]. On-chip antennas fabricated using a standard CMOS technology however suffer from poor radiation efficiency (<10%) and poor gain (<10 dBi) performance resulting from high substrate loss and surface wave effects [5], [6].

Several techniques have been previously investigated to improve on-chip antenna performance, which include high-resistivity silicon substrate [7], micro-machining [8], and artificial magnetic conductor [9]. With these techniques the antenna gain is limited to 1.5dBi, and in some cases the design and fabrication process is significantly more complex. Other techniques such as a dielectric lens-based on-chip antenna [10] and an on-chip horn antenna [11] have raised the radiation efficiency to 60% and the gain up to 8dBi. The shortfall of these techniques is the need for an external back-end-of-line (BEOL) process and a larger chip footprint.

In this paper, the feasibility of a low-cost on-chip dielectric resonator antenna (DRA) is investigated. With the proposed technique the radiation efficiency achieved is 45.7% and the gain of 4.5dBi. The antenna is simple to assemble and has a relatively small footprint of  $400\times400\times135~\mu m^3$ . The stacked dielectric resonators (DRs) improve the frequency bandwidth and the radiation performance over the frequency range of 0.45-0.47 Terahertz.

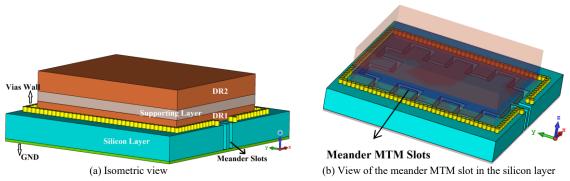

#### II. PROPOSED THZ DOUBLE-DR ON-CHIP ANTENNA ARRAY BASED ON MTM

Fig.1 shows the configuration of the proposed on-chip stacked DRA array. It consists of a silicon base with a ground-plane layer, two dielectric resonators (DRs), and a supporting layer that sandwiches the two DRs. The structures are secured with Epoxy glue. The feed structure is a meandering slot with a width of  $10\mu m$  that is fabricated in the silicon base, which has a thickness of  $50\mu m$ . It is shielded by the bottom ground plane conductor and connected to a 50-ohm grounded coplanar waveguide (GCPW) with line width of  $10\mu m$ . The meandering slot is surrounded by a rectangular metal wall made of stacked vias to prevent energy dissipation. The meander slots and metallic via wall act as series left-handed (LH) capacitors ( $C_L$ ) and shunt LH inductances ( $L_L$ ), respectively, to actualize metamaterial properties and thereby reduce the antenna dimensions and improve its performance [12][13].

The first dielectric resonator (DR1) is mounted on the surface of the substrate to form a traditional on-chip DRA. Second dielectric resonator (DR2) is arranged above the antenna in the vertical direction (x-axis) forming a series-fed linear array. The dielectric constant of the dielectric resonators is selected to be  $\varepsilon_r$ =10. Instead of the air gap, a low permittivity support layer is placed between DR1 and DR2 to help minimize the influence of the electromagnetic distribution between the DRs, shown in Fig.1. For multiple DR antenna structures, additional DRs can be stacked in the vertical direction (refer to Fig.1), with low permittivity supporters inserted between the DRs. In the proposed array design, the two DRs resonate at the same frequency of  $f_0$ =455 GHz, i.e. the dominant mode ( $TE_{\delta II}^x$  mode). With the specified design frequency,  $f_0$ =455 GHz, the dimensions of each DR having a dielectric constant of  $\varepsilon_r$  can be determined using the traditional truncated dielectric waveguide model [16] or a simplified engineering formula presented in [17]. Dimensions of the on-chip antenna structure comprising the series-fed double dielectric resonator antenna arrays are tabulated in Table I.

| TARI | FI  | STRUCT | TRAI | PARAN | /FTFR | DIMENSIONS |

|------|-----|--------|------|-------|-------|------------|

| IADL | ıı. | SINCLI | UKAL |       |       | DIMENSIONS |

| Series Feed On-Chip | Si-Layer  | GND       | Via      | Via       | DR1       | SL        | DR2        | Wslots |

|---------------------|-----------|-----------|----------|-----------|-----------|-----------|------------|--------|

| Antenna size        | thickness | thickness | diameter | thickness | thickness | thickness | thickness  |        |

| 400×400×135 μm³     | 50 μm     | 5 μm      | 5 μm     | 10 μm     | 20 μm     | 20 μm     | $40 \mu m$ | 10 μm  |

In the proposed series-feed antenna array most of the electromagnetic (EM) energy is initially coupled to DR1 from the on-chip meandering slot feeding structure. DR1 radiates its dominated mode  $TE_{\delta II}^x$  with high efficiency thereby acting as a traditional on-chip DRA. A portion of this energy is serially coupled to the upper DR2 to excite the  $TE_{\delta II}^x$  mode. The series coupling excitation leads to  $180^\circ$  phase change of the electromagnetic waves between the two dielectric resonators.

Fig.1. Layout of the proposed series fed double DR on-chip antenna array based on MTM.

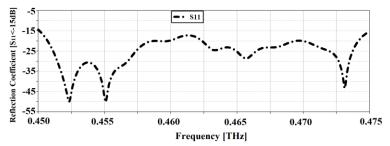

The S-parameter response of the reflection coefficient of the proposed series-fed double DR on-chip antenna array is shown in Fig. 2. The proposed on-chip antenna operates over a wide frequency range from 0.450 to 0.475 THz for  $S_{11}$ <-15dB, which corresponds to a fractional bandwidth of 5.4%. The average impedance match over its operational frequency range is around 30dB.

Fig.2. Reflection coefficient response. The impedance bandwidth is defined for  $S_{11}$ <-15dB.

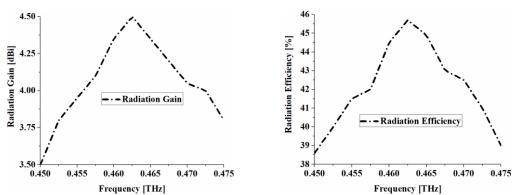

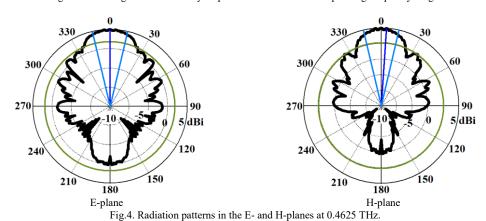

The radiation-gain and efficiency response of the proposed on-chip antenna versus frequency are shown in Fig. 3. Maximum gain and efficiency occur at around 0.4625 THz, which are 4.5dBi and 45.7%, respectively. Over the antenna's operating frequency range the minimum gain and efficiency are 3.5dBi and 38.6%, respectively, and the average gain and efficiency are ~3dBi and ~41.5%, respectively. The radiation E- and H-

planes patterns of the proposed on-chip antenna at operating frequency of 0.4625 THz are shown in Fig. 4. The antenna radiates predominately unidirectionally in both E- and H-planes with similar 3 dB beamwidth.

Fig.3. Radiation gain and efficiency response over the antenna's operating frequency range.

III. CONCLUSION

An on-chip antenna design is shown to exhibit an optimum gain and efficiency of 4.5dBi and 45.7%, respectively, at 0.4625 THz. The proposed antenna was fabricated using a standard CMOS technology. The proposed antenna array consisted of stacked dielectric resonators on top of a silicon substrate with meandering slot feed-line and the periphery of the silicon substrate is surround with metallic to prevent substrate loss and surface wave effects.

### ACKNOWLEDGEMENT

This work is partially supported by innovation programme under grant agreement H2020-MSCA-ITN-2016 SECRET-722424 and the financial support from the UK Engineering and Physical Sciences Research Council (EPSRC) under grant EP/E0/22936/1.

#### REFERENCES

- D. Hou, Y.-Z. Xiong, W-L. Goh, S. Hu, W. Hong, and M. Madihian, "130-GHz On-Chip Meander Slot Antennas with Stacked Dielectric Resonators in Standard CMOS Technology," IEEE Trans. Antennas Propag., vol. 60, no. 9, pp.4102-4109, Sep. 2012.

K. K. O. et al., "On-chip Antennas in Silicon ICs and Their Application," IEEE Trans. Electron Devices, vol. 52, no. 7, pp. 1312–1323, Jul.

- [2] K. K. O. et al., "On-chip Antennas in Silicon ICs and Their Application," IEEE Trans. Electron Devices, vol. 52, no. 7, pp. 1312–1323, Jul 2005.

- [3] B. Razavi, "Design of Millimeter-wave CMOS Radios: A Tutorial," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 56, no. 1, pp. 4–16, Jan. 2009.

- [4] P. V. Bijumon, Y. Antar, A. P. Freundorfer, and M. Sayer, "Dielectric Resonator Antenna on Silicon Substrate for System On-Chip Applications," IEEE Trans. Antennas Propag., vol. 56, no. 11, pp. 3404–3410, Nov. 2008.

- [5] Y. P. Zhang, M. Sun, and L. H. Guo, "On-Chip Antennas for 60-GHz Radios in Silicon Technology," IEEE Trans. Electron Devices, vol. 52, no. 7, pp. 1664–1668, Jul. 2005.

- [6] S. S. Hsu, K. C. Wei, C. Y. Hsu, and R.-C. Huey, "A 60-GHz Millimeter-Wave CPW-Fed Yagi Antenna Fabricated by Using 0.18- CMOS Technology," IEEE Electron Device Lett., vol. 29, no. 6, pp. 625–627, Jun. 2008.

- [7] E. Ojefors, E. Sonmeza, S. Chartier, P. Lindberg, A. Rydberg, and H. Schumacher, "Monolithic Integration of a Folded Dipole Antenna with a 24-GHz Receiver in SiGe HBT Technology," IEEE Trans. Microw. Theory Tech., vol. 55, no. 7, pp. 1467–1475, Jul. 2007.

- E. Ojefors, H. Kratz, K.Grenier, R. Plana, and A.Rydberg, "Micromachined Loop Antennas on Low Resistivity Silicon Substrates," IEEE Trans. Antennas Propag., vol. 54, no. 12, pp. 3593-3601, Dec. 2006.

- Antennas Propag., vol. 34, no. 12, pp. 3593–3601, Dec. 2006.

[9] K. Kang, F. Lin, D. D. Pham, J. Brinkhoff, C. H. Heng, Y. X. Guo, and X. Yuan, "A 60-GHz Receiver with an On-Chip Antenna in 90 nm CMOS," IEEE J. Solid-State Circuits, vol. 45, no. 9, pp. 1720–1731, Sep. 2010.

[10] A. Babakhani, G. Xiang, A. Komijani, A. Natarajan, and A. Hajimiri, "A 77-GHz Phased-Array Transceiver with On-Chip Antennas in Silicon: Receiver and Antennas," IEEE J. Solid-State Circuits, vol. 41, no. 12, pp. 2795–2806, Dec. 2006.

[11] Y. C. Ou and G. M. Rebeiz, "On-Chip Slot-Ring and High-Gain Horn Antennas for Millimeter-Wave Wafer-Scale Silicon Systems," IEEE Trans. Microw. Theory Tech., vol. 59, no. 8, pp. 1963–1972, Aug. 2011.

[12] M. Alibakhshi-Kanari, M. Naser-Monhadas, R. A. Sadagharadab, B. S. Virdee and E. Limiti, "Periodic Array of Complementary Artificial

- [12] M. Alibakhshi-Kenari, M. Naser-Moghadasi, R. A. Sadeghzadeh, B. S. Virdee and E. Limiti, "Periodic Array of Complementary Artificial Magnetic Conductor Metamaterials-Based Multibade Multibade of Broadband Wireless Transceivers," IET Microwaves, Antennas & Propagation, Vol. 10, Issue 15, 10 Dec. 2016, p. 1682 – 1691.

- [13] M. Alibakhshi-Kenari, M. Naser-Moghadasi and R. Ali Sadeghzadeh, "Composite Right-Left-Handed-Based Antenna with Wide Applications in Very-High Frequency-Ultra-High Frequency Bands for Radio Transceivers," IET Microwaves, Antennas & Propagation, Vol. 9, Issue 15, 10 Dec. 2015, p. 1713 – 1726.