## ESCUELA TÉCNICA SUPERIOR DE INGENIEROS INDUSTRIALES Y DE TELECOMUNICACIÓN

Titulación:

INGENIERO DE TELECOMUNICACIÓN

Título del proyecto:

"DISEÑO DE UN CONTROL AUTOMÁTICO DE GANANCIA CMOS PARA RECEPTORES INALÁMBRICOS DE BAJO CONSUMO"

> Aritz Redin Ilarregui Tutor: Antonio J. López Martín Pamplona 3 de abril de 2014

#### **Agradecimientos**

- En primer lugar a mi tutor, Antonio, por el proyecto que me ofreció y porque que a pesar de tener una agenda apretada siempre esta en el laboratorio cuando se le necesita y su velocidad resolviendo las dudas y problemas que me iban surgiendo es impresionante.

- A Coro, Fermin, Jesus y toda la gente del laboratorio que siempre están dispuestos a ayudar y han hecho que me sienta a gusto en mi puesto.

- A mis padres, que me han apoyado incondicionalmente y siempre están dispuestos a escuchar como avanza mi proyecto.

- A Edurne, que poco a poco ya va entendiendo de que va esto de la electrónica y además ha soportado todas mis tonterías siempre que salía del laboratorio saturado.

- A Miguel, Adrian, David, Mikel y Hector por amenizarme los almuerzos.

- A Robert Donner por inventar el Buscaminas que tanto me ha entretenido cuando hacia simulaciones largas.

#### Índice

| Motivación y objetivos                       | 5  |

|----------------------------------------------|----|

| Marco del proyecto                           | 5  |

| Objetivos del proyecto                       | 6  |

| Técnicas de diseño                           | 8  |

| Transistores de puerta flotante (FGM)        | 8  |

| Transistores de puerta cuasi-flotante (QFGM) | 11 |

| Clase AB                                     | 14 |

| Diseño del bloque básico                     | 16 |

| Introducción a los transconductores          | 16 |

| Diseños básicos                              | 17 |

| Elementos del amplificador                   | 19 |

| Seguidor de tensión                          | 19 |

| Seguidor de corriente                        | 22 |

| Resistencias                                 | 22 |

| Amplificador completo                        | 23 |

| Dimensionamiento                             | 24 |

| Simulaciones                                 | 25 |

| Diseño del control de ganancia               | 29 |

| Descripción de Técnicas                      | 29 |

| Control activo por medio de transistores     | 29 |

| Array de resistencias pasivas                | 30 |

| Control de ganancia                          | 31 |

| Alternativa del elevador al cuadrado         | 31 |

| Alternativa del detector de pico             | 37 |

| Amplificador de ganancia programable         | 45 |

| Respuesta transitoria                        | 46 |

| THD                                          | 53 |

| Ancho de banda                               | 54 |

| Intermodulación de tercer orden              | 55 |

| Factores de rechazo                          | 56 |

| Resumen de parámetros           | 57 |

|---------------------------------|----|

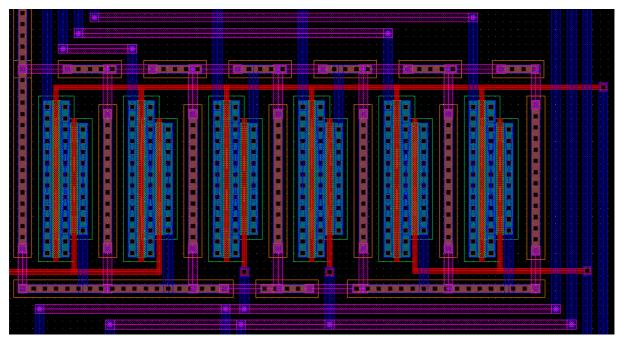

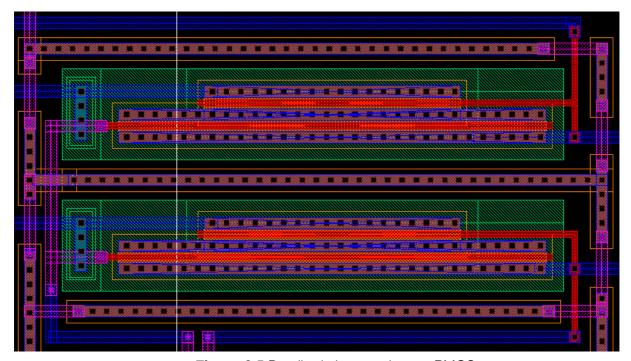

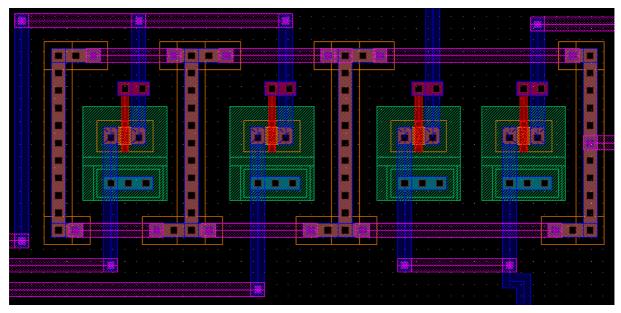

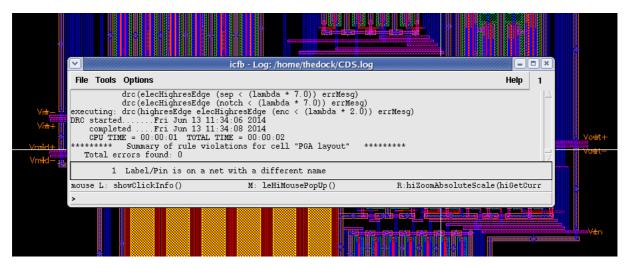

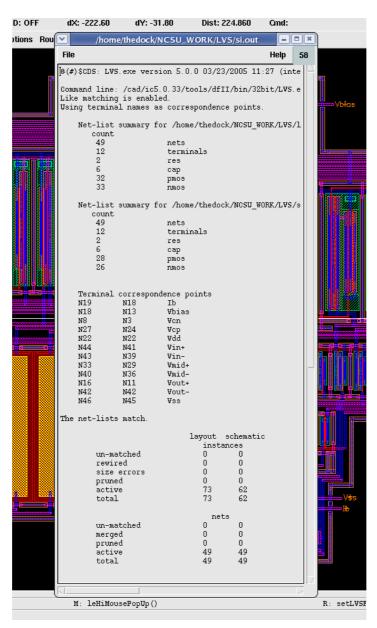

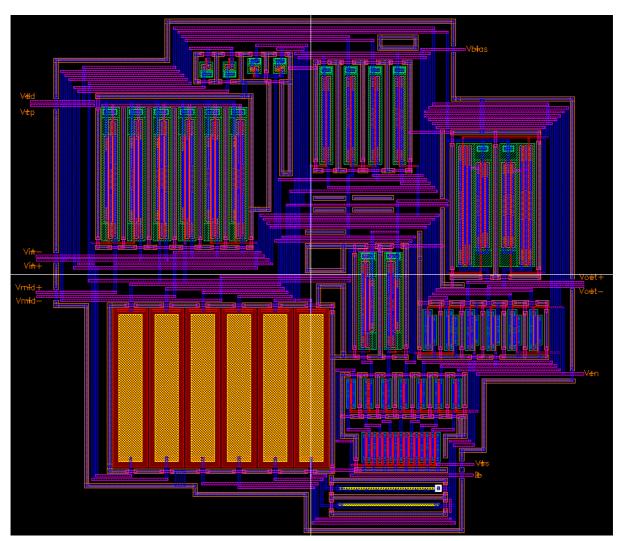

| Técnicas y diseño del layout    | 59 |

| Técnicas de diseño del layout   | 59 |

| Layout del sistema              | 60 |

| Conclusiones y líneas de futuro | 67 |

| Conclusiones                    | 67 |

| Líneas de futuro                | 68 |

| Bibliografía                    | 70 |

| Libros                          | 70 |

| Artículos                       | 70 |

## Capítulo 1 Motivación y objetivos

#### Marco del proyecto

La necesidad y por tanto la demanda actual de circuitos de bajo consumo es muy alta debido a la tendencia tecnológica de conectar todo y tener sistemas autónomos. Estos sistemas autónomos toman su energía del medio por lo que la eficiencia energética de los circuitos que tengan que alimentar es vital.

Esta necesidad se traduce en una reducción de las tensiones de alimentación y las corrientes de polarización de los circuitos *CMOS* sin esperar por ello un empeoramiento de su comportamiento. Los circuitos se han adaptado perfectamente a estas necesidades gracias al modo en que se procesan las señales. Los diseños mixtos, es decir, con parte analógica y parte digital son los más extendidos ya que con ellos se consigue integrar toda la electrónica en un mismo chip. La parte más perjudicada por esta reducción de las alimentaciones es la parte analógica y es la que va a necesitar de nuevas técnicas para seguir ofreciendo un rendimiento óptimo.

Con este proyecto se pretende acometer del diseño y fabricación en silicio de un nuevo sistema de Control Automático de ganancia de muy bajo consumo y de aplicación en receptores de comunicaciones inalámbricas que requieran consumos muy reducidos, como pueden ser los de tecnología ZigBee o NFC. Estos receptores son necesarios en aplicaciones incipientes destinadas a la creación de ambientes inteligentes (hogar, oficina, automóvil),

conectividad inalámbrica de dispositivos (*PCs*, *PDAs*, teléfono móvil, navegadores *GPS*, cámaras digitales, etc.) o monitorización médica remota. Tales aplicaciones son prioritarias en el VII Programa Marco de la UE, reflejo de la enorme demanda esperada de estas tecnologías y la urgencia del liderazgo europeo en ellas. El circuito a desarrollar supone un reto tecnológico al combinar la necesidad de baja tensión, bajo consumo y altas prestaciones. Se pretende con este proyecto lograr un salto cualitativo en el estado del arte en cuanto a consumo y prestaciones.

Las tecnologías de silicio CMOS a utilizar son avanzadas (≤0.5µm) y el rango de tensiones de alimentación reducido (≤3.3V). El bajo consumo y las altas prestaciones, son los requisitos de los recientes estándares de comunicaciones inalámbricas de corta distancia (Bluetooth 4.0, ZigBee, NFC, etc.). La demanda de bajo coste está impulsando soluciones single-chip basadas en nuevas arquitecturas de receptores Low-IF y Zero-IF altamente integrados, donde los problemas asociados al procesado en IF y banda base manteniendo bajo consumo, bajo ruido y alta linealidad han convertido esta sección del receptor en un elemento crítico del sistema. En este proyecto se aplicarán novedosas técnicas de diseño en baja tensión y bajo consumo para lograr un salto cualitativo en el control automático de ganancia necesario en receptores inalámbricos en términos de minimización del consumo de potencia.

El resultado más tangible del proyecto será un bloque que controle la ganancia de un sistema automáticamente adaptado a las especificaciones de las tecnologías inalámbricas actuales, simulado mediante el entorno *Cadence*. El bloque constara de subbloques con funciones específicas El diseño de estos sistemas es uno de los mayores retos a los que se enfrenta la industria microelectrónica actual de acuerdo con las previsiones de la *Semiconductor Industry Association (SIA)*, dada la dificultad de conjugar el bajo consumo demandado por el uso de baterías o energía del entorno, la necesidad de baja tensión de alimentación impuesta por las tecnologías microelectrónicas modernas, y las altas prestaciones demandadas por las aplicaciones inalámbricas actuales. Dado el alto interés industrial y social de estas tecnologías, es asimismo una de las áreas prioritarias en el VII Programa Marco de la Unión Europea.

El proyecto pretende contribuir en el desarrollo de nuevas arquitecturas para control automático de ganancia en secciones de *IF* en receptores *Low-IF* que minimicen el consumo. Incluye entre otros el desarrollo de amplificadores clase AB, detectores de pico y convertidores *A/D*. Se aplicarán las técnicas más recientes generadas en la *UPNa* (circuitos quasi-floating gate, etc.) en pos de una reducción sustancial del consumo.

#### Objetivos del proyecto

De acuerdo a lo dispuesto hasta ahora los objetivos del proyecto son los siguientes:

- Familiarizarse con el entorno *Cadence*, utilizado para el diseño de circuitos electrónicos y estudiar las múltiples posibilidades que ofrece.

- Diseñar un transconductor que sirva como bloque base para el amplificador y posteriormente diseñar una configuración que permita alcanzar los valores de ganancia y linealidad deseados.

- Diseñar el control automático de ganancia evaluando varias técnicas para finalmente seleccionar la que mejores resultados ofrezca.

- Una vez terminadas las dos partes anteriores juntarlas para obtener un bloque que realice la tarea completa.

- Habiendo dimensionado bien el circuito para minimizar el área de silicio ocupada, realizar un layout para el esquema principal que optimice el funcionamiento en el mínimo espacio con el fin de mejorar la escala de integración.

- Simular el comportamiento tanto del esquemático como del layout con el entorno Cadence para comprobar su correcto funcionamiento.

## Capítulo 2 Técnicas de diseño

Las tendencias actuales en el diseño microelectrónico en tecnologías CMOS, referidas sobre todo a temas de fiabilidad y consumo de potencia, como la reducción del grosor puertaóxido, el aumento en la densidad de integración, o la mayor demanda de equipos "portables" que funcionen con pilas o baterías, han forzado la disminución de las tensiones de alimentación y su aproximación a los umbrales de los transistores MOS, así como un bajo consumo de potencia por parte de los equipos al mismo tiempo.

En el caso de los circuitos CMOS analógicos que emplean técnicas convencionales, esta reducción drástica de las tensiones de alimentación va a suponer una degradación del rango dinámico y de la relación señal a ruido. Para paliar estos problemas, se deben emplear una serie de técnicas alternativas destinadas específicamente a trabajar con tensiones de alimentación bajas, y que permiten operar con señales rail-to-rail.

#### Transistores de puerta flotante (FGM)

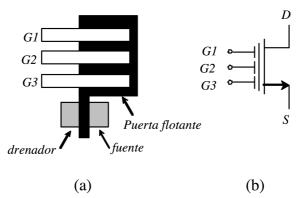

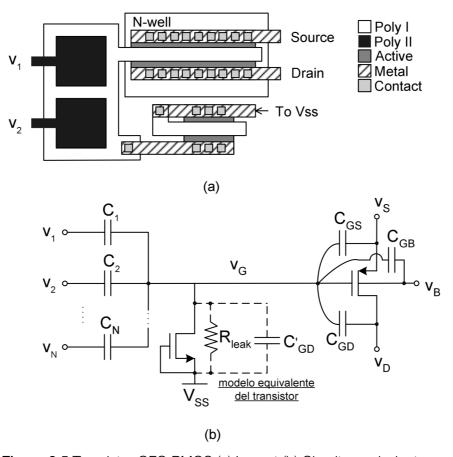

El transistor MOS de puerta flotante (o FGT: Floating Gate Transistor) de n entradas se caracteriza por el hecho de que el electrodo de puerta que se extiende sobre el canal queda flotando, de modo que su tensión viene determinada por una cadena de n puertas de control que se sitúan sobre ese electrodo empleando una segunda capa de polisilicio, y que forman n

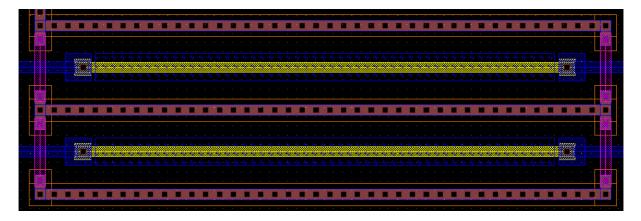

condensadores sobre los cuales se aplicarán las distintas tensiones de entrada. Un ejemplo de esas puertas múltiples lo tenemos en el sencillo layout de la figura 2.1.

Figura 2.1 (a) Layout de un FGT de 3 entradas (b) Símbolo

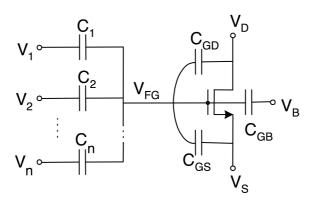

Esta configuración deja un circuito equivalente como el de la siguiente figura. Cabe destacar que además de las capacidades de las puertas flotantes se han añadido también las capacidades parásitas del transistor.

Figura 2.2 Circuito equivalente de un FGMOS de n entradas

Dado que la puerta flotante no es capaz teóricamente de cargarse ni de descargarse, la carga inicial que se almacene en ella se va a conservar. Esta carga podrá ser eliminada por diferentes métodos así que la consideraremos nula para el análisis. La tensión de la puerta flotante del transistor responde a la siguiente expresión:

$$V_{FG} = \frac{\sum_{k=1}^{n} C_k V_k + C_{GS} V_S + C_{GB} V_B + C_{GD} V_D}{C_T}$$

(2.1)

CT es la suma de todas estas capacidades, no obstante las capacidades parásitas del transistor son mucho menores que las elegidas para las puertas por lo que:

$$C_T = \sum_{k=1}^{n} C_k + C_{GS} + C_{GB} + C_{GD} \approx \sum_{k=1}^{n} C_k$$

(2.2)

De estas dos expresiones se deduce que la tensión en la puerta del transistor es una suma ponderada de todas las tensiones de entrada. Los coeficientes ( $a_k$ ) que ponderan esta suma son los cocientes entre las capacidades de cada entrada y la capacidad total más algún término debido a las capacidades parásitas:

$$V_{FG} = a_1 \cdot V_1 + a_2 \cdot V_2 + \dots + a_n \cdot V_n + \frac{C_{GS}}{C_T} \cdot V_S + \frac{C_{GD}}{C_T} \cdot V_D + \frac{C_{GB}}{C_T} \cdot V_B$$

(2.3)

$$a_k = \frac{C_k}{C_T} \approx \frac{C_k}{\sum_{i=1}^n C_i}$$

(2.4)

Todas las entradas se ven atenuadas debido a que la conexión es un divisor de tensión capacitivo, lo que permite dimensionales para poder utilizar señales *rail-to-rail*, muy importantes en aplicaciones de baja tensión de alimentación.

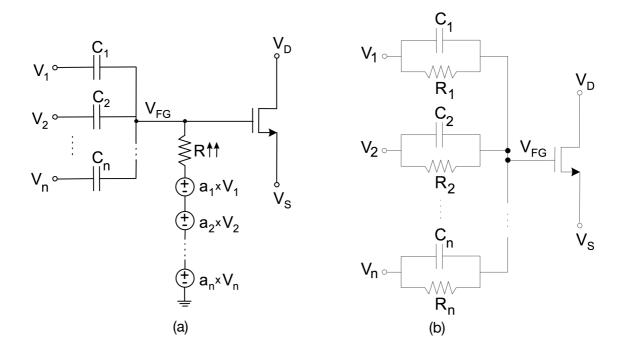

Las ventajas de estas puertas flotantes son evidentes, pero también tienen ciertas desventajas en forma de problemas de simulación, ya que la mayoría de entornos software sustituyen los condensadores por circuitos abiertos al realizar los análisis en *DC*, lo que provoca problemas de convergencia en estos nodos.

Figura 2.3 Segundo modelo de simulación para evitar problemas de convergencia

Se pueden solucionar de distintas maneras, como vemos en la figura 2.3 (a) se podría optar por conectar n fuentes de tensión controladas por tensión (VCVS) a la puerta flotante en cuestión, de forma que las tensiones de control de las mismas sean las distintas tensiones de entrada ( $V_k$ ), y la ganancia asociada a cada una de las fuentes sea su coeficiente de ponderación correspondiente ( $a_k$ ). Estas fuentes dominarían el comportamiento del sistema solo en DC evitando el problema de convergencia y sin afectar a la respuesta AC por medio de la

resistencia R de gran valor. Otra aproximación es colocar una resistencia también muy grande en paralelo con cada condensador como se ve en la figura 2.3 (b).

En este caso (b) hay que elegir las resistencias de tal manera que cada rama de entrada tenga el mismo peso que antes de colocarlas, por lo tanto deberán cumplir lo siguiente:

$$a_i = 1 + \frac{R_i}{R_T} \tag{2.5}$$

Donde  $R_T$  es el paralelo de las resistencias correspondientes a todas las demás entradas.

Una conclusión que podemos extraer de esto es que la aplicación más inmediata de los FGM es la de generar combinaciones lineales de tensiones de manera sencilla. Otra posible aplicación es conservar la carga inicial de los condensadores a largo plazo lo que abre el camino para que sean utilizados como almacenamiento de información. Por último permiten atenuar la señal de entrada consiguiendo así un mayor rango de entrada en los circuitos que operan contenciones de alimentación bajas. Además permite controlar también el nivel en DC a la entrada del transistor.

#### Transistores de puerta cuasi-flotante (QFGM)

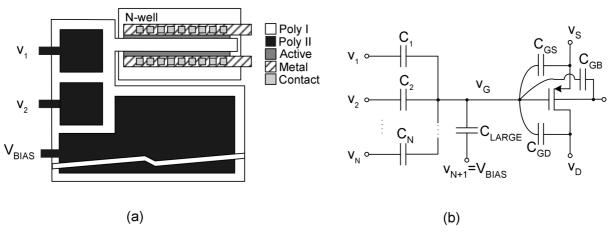

Surge ahora el concepto de *MIFG* (Multiple input Floating Gate). A partir de él se va a obtener el modelo *QFGM* y por tanto hay que estudiar sus ventajas y desventajas.

En la siguiente figura se muestra un MIFG de 3 entradas:

Figura 2.4 Transistor MIFG pMOS (a) Layout (b) Circuito equivalente

Estando los terminales de entrada acoplados capacitivamente y considerando que su carga almacenada es nula, la tensión viene dada por la siguiente expresión:

$$v_G = \frac{1}{C_T} \left( \sum_{k=1}^{N+1} C_k v_k + C_{GS} v_S + C_{GB} v_B + C_{GD} v_D \right)$$

(2.6)

donde  $C_k$  es la capacidad de la rama k-ésima y  $C_T$  viene dado por:

$$C_T = \sum_{k=1}^{N+1} C_k + C_{GS} + C_{GB} + C_{GD}$$

(2.7)

Hasta aquí el análisis es idéntico al de los FGM así que llegamos a las mismas conclusiones haciendo posible la utilización de señales rail-to-rail, es decir, que abarquen tensiones desde  $V_{SS}$  hasta  $V_{dd}$ .

Otro requisito de este tipo de circuitos es mantener la tensión DC de la puerta flotante cercana a una de las dos tensiones de alimentación para una correcta polarización del transistor. Se debe mantener cercana a  $V_{dd}$  si el transistor es un MIFG NMOS, y cercana a  $V_{SS}$  si es un MIFG PMOS. Por esta razón, la entrada  $V_{N+1}$ , que aparece en la figura 2.4 (b), se fija a una tensión DC llamada  $V_{BIAS}$ , que adoptará el valor  $V_{dd}$  o  $V_{SS}$  dependiendo del tipo de transistor que sea. El valor del condensador de acoplo ( $C_{LARGE}$ ) asociado a esta entrada, debe ser mucho mayor que los demás. Por tanto, la ecuación 2.6 pasa a tomar esta forma:

$$v_G = \frac{C_{LARGE}}{C_T} V_{BIAS} + \frac{1}{C_T} \left( \sum_{k=1}^{N+1} C_k v_k + C_{GS} v_S + C_{GB} v_B + C_{GD} v_D \right)$$

(2.8)

Hay que mencionar que el empleo de transistores *MIFG* presenta una serie de desventajas detalladas a continuación:

- Los condensadores almacenan la carga durante periodos de tiempo muy largos así que es necesario evitarlo mediante fabricación o descargarlos posteriormente por métodos de borrado de memoria. Este problema también lo presentan los *FGM*.

- ullet El área de silicio utilizada crece considerablemente debido a las grandes dimensiones del condensador de desacoplo  $C_{LARGE}$ .

- Si los transistores *MIFG* forman parte del par diferencial de entrada de un amplificador, el condensador de desacoplo *C<sub>LARGE</sub>* hará que el producto *ganancia por ancho de banda* se vea sensiblemente reducido.

Estos problemas se pueden solucionar empleando una resistencia de gran valor (*R<sub>leak</sub>*) para conectar la puerta flotante a la tensión DC de polarización correspondiente, en lugar del condensador *C<sub>LARGE</sub>*. Mediante esta sustitución se obtiene un *transistor de puerta cuasi-flotante* (*Quasi-Floating Gate Transistor*), que se puede observar en la figura 2.5.

Como en el caso de los FGT, los terminales de entrada están acoplados capacitivamente a la puerta cuasi-flotante pero, en este caso, la tensión DC de la puerta se fija a  $V_{SS}$ , dado que el transistor es PMOS, sin necesidad de un condensador de gran valor, sino con una resistencia. En la práctica, esta resistencia de gran valor puede implementarse mediante un transistor NMOS de tamaño mínimo operando en la región de corte, lo cual puede conseguirse cortocircuitando los terminales de puerta y fuente. Esto supondrá un ahorro considerable en términos de área,

Figura 2.5 Transistor QFG PMOS (a) Layout (b) Circuito equivalente

siendo necesaria una superficie de silicio mucho menor que la ocupada por el condensador  $C_{LARGE}$ .

La nueva tensión de puerta es y la nueva capacidad total son:

$$V_G = \frac{sR_{leak}}{1 + sR_{leak} C_T} \left( \sum_{k=1}^{N} C_k V_k + C_{GS} V_S + C_{GB} V_B + C_{GD} V_D \right)$$

(2.9)

$$C_T = \sum_{k=1}^{N+1} C_k + C_{GS} + C_{GD} + C_{GB} + C'_{GD}$$

(2.10)

De la expresión 2.9 obtenemos que la tensión en la puerta sufre un filtrado paso alto. Sin embargo la frecuencia de corte es tan baja que siempre vamos a tener una suma ponderada tal y como la teníamos antes. Acerca de  $R_{leak}$ , cabe destacar que ni su valor exacto ni su dependencia con la tensión o la temperatura son factores importantes ya que va a ser lo suficientemente grande como para que la frecuencia de corte que fije sea lo suficientemente baja.

En los transistores QFGT, la resistencia  $R_{leak}$  establece una tensión DC en la puerta del transistor igual a la tensión DC que se haya aplicado en su terminal, y sobre ella se superpone la

tensión AC de la expresión 2.9 producida por el resto de entradas. De este modo, la tensión de puerta puede ser menor que la tensión de alimentación negativa, lo cual es bastante común cuando el circuito está alimentado con tensiones inferiores a 1 V. Esto no va a suponer ningún problema, mientras la diferencia de potencial entre la tensión de puerta y la de alimentación sea menor que la tensión que provoca que la unión P-N entre el cuerpo y la fuente del transistor NMOS con el que se ha implementado  $R_{leak}$  se polarice en directa y, por lo tanto, empiece a conducir. Para controlar este problema, basta con escoger ratios entre los condensadores de acoplo de las entradas muy precisos, a la hora de decidir los valores de los mismos.

El análisis para un transistor QFGT NMOS es similar. En ese caso, la resistencia se conecta a  $V_{DD}$ , y se implementa mediante un transistor PMOS en corte.

#### Clase AB

Otra de las técnicas que se va a emplear en este proyecto, con el fin de mejorar las prestaciones del amplificador y que así responda a las especificaciones de la aplicación, es el diseño de circuitos cuya operación sea en clase AB, en lugar de en clase A. Para conseguir la operación en clase AB a partir de circuitos que operen en clase A, se van a utilizar los transistores de puerta cuasi-flotante (QFGT) que se han explicado en el apartado anterior.

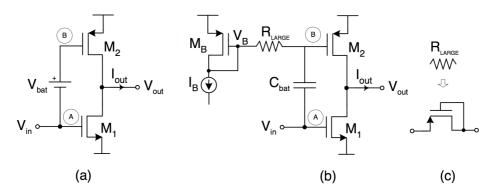

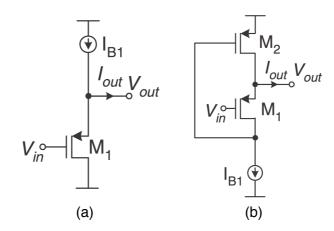

La siguiente figura detalla los esquemas básicos de la configuración en clase AB:

Figura 2.6 Etapa básica en clase AB (a) Con batería flotante (b) Con QFGT para implementar la batería (c) Posible implementación de la R<sub>large</sub>

El uso de la batería flotante permite al nodo B seguir las variaciones del nodo A con una variación de  $V_{bat}$  Voltios. En ausencia de señal, la corriente la establece la tensión en DC del nodo A más  $V_{bat}$ , y en presencia de señal las variaciones del nodo A se transfieren a B permitiendo que la corriente de salida no esté limitada por la corriente en condiciones estáticas.

En la figura 2.6 (b) la corriente en condiciones estáticas va a ser  $I_b$  dado que la batería se va a comportar como un circuito abierto, sin embargo, cuando introducimos señal al sistema la tensión en A se va a transferir a B tras un filtrado paso alto de muy baja frecuencia de corte de forma que únicamente la componente en DC es bloqueada en ese camino. No se van a explicar más circuitos en clase AB sino que se verán ya aplicados a los esquemáticos del proyecto.

Una gran ventaja de estos circuitos es la mejora en el *Slew-Rate* cuando el circuito opera en *gran señal*. Sin embargo, al operar en pequeña señal, la tensión a la salida también será pequeña y, por tanto, no será necesaria una gran cantidad de corriente en el condensador de carga para establecerla. Esto significa que, en estas circunstancias, aunque la corriente de polarización sea baja, el parámetro del *Slew-Rate* no se va a ver afectado.

En los circuitos con topología en clase A, la corriente de salida está limitada por la corriente de polarización  $I_B$ , siendo ésta la máxima que se puede alcanzar. Por tanto, el valor máximo del Slew-Rate será  $SR_{max} = I_B / C_L$  (Siendo  $C_L$  una carga capacitiva). En pequeña señal esto no supone un gran problema, ya que se puede conseguir un buen funcionamiento del sistema con corrientes de polarización relativamente pequeñas. Sin embargo, cuando la operación es en gran señal, se tendrán que fijar valores de  $I_B$  altos para poder conseguir que el  $I_B$  aumento de la corriente de polarización conllevará, a su vez, un aumento del consumo de potencia. Aquí reside precisamente la ventaja de emplear circuitos con topología en clase  $I_B$ 0. En estos circuitos, en presencia de señal a la entrada, la corriente de salida no está limitada a  $I_B$ 1, sino que puede ser mayor. De este modo, permite que el valor del Slew-Rate sea alto manteniendo un consumo de potencia bajo.

Por lo tanto, se puede concluir que, en operación en gran señal, es conveniente emplear un circuito con topología AB frente al equivalente con topología A, ya que así la velocidad del sistema es mayor y tiene una respuesta más adecuada frente a variaciones rápidas de señal (componentes frecuenciales altas).

### Capítulo 3

#### Diseño del bloque básico

#### Introducción a los transconductores

Dentro de los amplificadores de señal podemos distinguir cuatro tipos en función de la magnitud que utilizan como entrada y salida, bien sea tensión o corriente.

El parámetro que define el tipo del amplificador es su ganancia, que es el cociente entre la magnitud de salida entre la de entrada. De esta manera, si ambas son tensiones se denomina amplificador de tensión y si ambas son corrientes se denomina amplificador de corriente. En estos dos tipos la ganancia es un parámetro adimensional. Cuando la entrada es en corriente y la salida en tensión, la ganancia tiene unidades de resistencia y se le llama amplificador de transresistencia. Por último el amplificador que utiliza entrada en tensión y salida en corriente se llama amplificador de transconductancia, ya que la ganancia tiene unidades de conductancia.

Un OTA es un amplificador operacional de transconductancia cuya relación entrada salida es la siguiente:

$$I_{out} = G_m \cdot V_{in} \tag{3.1}$$

La principal diferencia entre un amplificador operacional y un OTA es la impedancia de salida, que es mucho mayor en el OTA, haciéndolo más adecuado para cargas resistivas

grandes o cargas capacitivas, mientras el amplificador operacional trabaja mejor cuando la carga es resistiva y pequeña.

De este comportamiento podemos extraer que en realidad un *OTA* es un amplificador operacional con un buffer a la salida que copia la tensión de salida del amplificador pero situando la impedancia de salida en un valor mucho más alto.

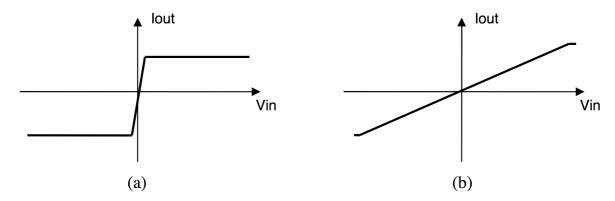

Idealmente podemos considerar un OTA como una fuente de corriente controlada por tensión, pero esto ocurre en un rango de tensiones de entrada muy pequeño y con una pendiente muy alta.

Figura 3.1 (a) Curva de transferencia de un OTA (b) Curva de transferencia de un transconductor

Para aplicaciones que requieran una conversión lineal en un rango más amplio de señal se utilizan *OTAs* linealizados, también llamados transconductores, que como se ve en la figura 3.1 tienen una pendiente mucho más suave y un rango de conversión lineal más amplio.

Los transconductores son los amplificadores más sencillos ya que el comportamiento propio del transistor lo hace idóneo para operar con entrada en tensión y salida en corriente. Se va a utilizar un *OTA* más adelante para otros bloques pero el diseño básico va a ser un amplificador de tensión. Para hacer esa conversión, la forma más sencilla es hacer circular la corriente de salida por una carga pasiva conectada a un nodo de referencia

#### Diseños básicos

Las dos cosas importantes a tener en cuenta al diseñar un *OTA* son que debe realizar una conversión tensión-corriente y que hay que llevar esa corriente obtenida hasta la salida del dispositivo.

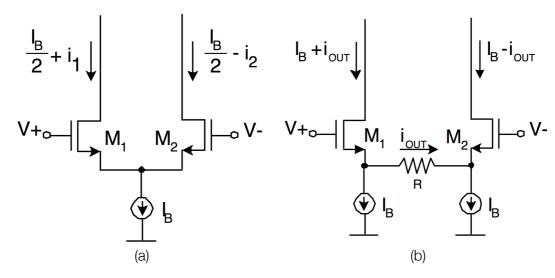

Como vemos en la figura 3.2 (a), la conversión tensión-corriente del OTA sencillo es esta:

$$i_{out} = i_1 + i_2 \approx G_m (V_+ - V_-) = G_m \cdot V_{in}$$

(3.2)

ya que consideramos los dos transistores iguales y por lo tanto sus transconductancias también van a serlo. Sin embargo, al ser la transconductancia un parámetro

muy grande, la corriente de salida enseguida se saturará al valor de la corriente de polarización  $I_B$  que es el máximo que puede dar esta configuración.

La transconductancia se puede modificar fácilmente variando la corriente de polarización.

Debido a las limitaciones del *OTA* básico será necesario linealizarlo, y para ello, el método más común es colocar un elemento pasivo entre los dos terminales de fuente de los transistores que forman el par diferencial, tal y como se ve en la figura 3.2 (b).

Figura 3.2 (a) OTA básico (b) Transconductor básico

Este método, conocido como degeneración de fuente, muestra una respuesta con una pendiente mucho más suave que el OTA original de forma que es apto para aplicaciones que exigen linealidad. Su conversión tensión-corriente es esta:

$$i_{od} = 2 \cdot i_{out} = i_1 + i_2 \approx 2 \cdot \frac{(V_+ - V_-)}{R} = 2 \cdot \frac{V_{in}}{R}$$

(3.3)

$$G_m = \frac{2}{R} \tag{3.4}$$

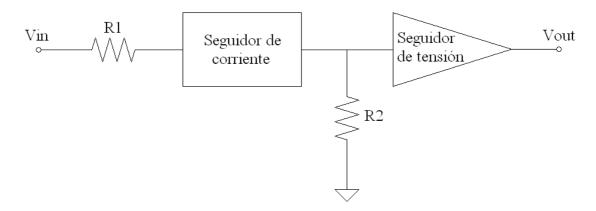

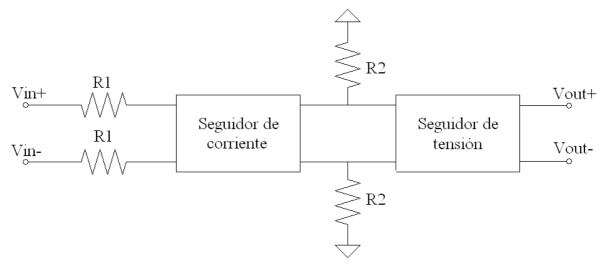

Sin embargo el amplificador definitivo parte de un diseño que consta de un seguidor de corriente y un seguidor de tensión. La tensión en el punto intermedio es la corriente generada por la tensión de entrada y la resistencia  $R_1$  multiplicada por la resistencia  $R_2$ . Además al ir conectado a la entrada de un seguidor de tensión se dará que la tensión de salida será igual a la del punto medio.

La ganancia de esta configuración viene dada por:

$$V_{out} = V_{mid} = i_{in} \cdot R_2 = \frac{V_{in}}{R_1} \cdot R_2$$

(3.5)

$$A = \frac{R_2}{R_1} \tag{3.6}$$

En este amplificador podemos controlar la linealidad haciendo  $R_1$  de mayor valor y su ganancia mediante el ratio de esas dos resistencias. Para el mismo voltaje de entrada, con una  $R_1$  mayor, la corriente que entra al sistema es más pequeña, por lo tanto estará más lejos de la corriente máxima que puede aceptar el mismo. El aumento de esta primera resistencia por lo tanto nos llevara a valores de THD a la salida más bajos.

Figura 3.3 Esquema básico del amplificador utilizado

Por otro lado, otra ventaja de este esquema es que es de ancho de banda constante, a diferencia de amplificadores más sencillos en los que lo que se mantiene constante es el producto ganancia por ancho de banda. Esto se debe a que se dan dos conversiones, una primera tensión-corriente y una segunda corriente tensión, ambas en elementos resistidos que limitaran el ancho de banda de la forma descrita anteriormente pero no dependiendo de la ganancia que este configurada.

#### Elementos del amplificador

El esquema que se va a utilizar en el amplificador principal consta como se ha descrito anteriormente de 2 elementos principales que son un seguidor de corriente y un seguidor de tensión. Además, para ajustar la ganancia se van a utilizar 2 pares de resistencias, uno para la rama positiva y otro para la negativa.

Dado que las aplicaciones a las que se ha orientado el dispositivo son de muy bajo consumo, lo idóneo aquí es utilizar una configuración en clase AB, que mejora el Slew-Rate del sistema y proporciona un consumo muy bajo cuando no existe señal a la entrada.

#### Seguidor de tensión

Un seguidor de tensión es básicamente un elemento que copia la tensión de entrada en el nodo de salida y proporciona potencia para que esa tensión no dependa de la impedancia de carga que se le conecte. Para ello es preciso una resistencia de salida pequeña, cosa que el seguidor de tensión sencillo de la figura 3.4 (a) no proporciona.

La resistencia de salida del seguidor invertido es mucho más pequeña pero, a pesar de ser muy utilizado en aplicaciones de baja tensión, tiene un gran inconveniente y es que su rango de tensiones de entrada y de salida es muy limitado.

Figura 3.4 (a) Seguidor de fuente (b) Seguidor de fuente invertido

Se necesita por lo tanto aproximaciones más complejas que resuelvan el problema con más solvencia. En la figura 3.5 (a) se muestra lo que se denomina súper seguidor de fuente (SSF) que consta únicamente de dos transistores como en la figura 3.4 (b) pero con otra disposición.

A pesar de haber mejorado el rango de entrada y salida, y la resistencia de salida respecto al seguidor de corriente original, este esquema sigue teniendo dos importantes desventajas. La primera es que la corriente máxima que puede suministrar a la carga esta limitada por la corriente de polarización y la segunda es que la rama adicional introducida incrementa el consumo en condiciones de reposo.

Estos dos problemas van a ser resueltos por la configuración en clase AB de la figura 3.5 (b). Este último esquema hace uso de las técnicas QFGT comentadas en el capítulo 2. Lo que se ha hecho es convertir la puerta del transistor  $M_4$  en flotante mediante el condensador

Figura 3.5 (a) Súper seguidor de fuente (b) Súper seguidor de fuente en clase AB

colocado entre las puertas de  $M_2$  y  $M_4$  y la resistencia  $R_{large}$  que fija la tensión en DC de la puerta de  $M_4$  a  $V_B$ .

Esto se ha realizado sin alterar el comportamiento en DC ya que el condensador no afecta en condiciones de reposo y no hay caída de tensión en la resistencia  $R_{large}$ . De esta manera, la corriente en reposo es controlada por el espejo que forman  $M_3$  y  $M_4$ .

En conclusión, la introducción de estos dos elementos no afecta al comportamiento estático pero permite la operación AB que mejora la respuesta dinámica. Para explicar el comportamiento del sistema suponemos un incremento en la tensión de entrada que provoca una bajada en la puerta de  $M_2$ . Esta bajada se propaga a la puerta de  $M_4$  debido al condensador flotante, que actúa como una batería no se descarga instantáneamente. Esto provoca que la  $V_{SG}$  de  $M_4$  aumente y lo haga también por tanto la corriente a través de su drenador. Al mismo tiempo la caída de tensión en la puerta de  $M_2$  hace decrecer la corriente en este transistor por debajo de la de polarización aumentando así la corriente de salida.

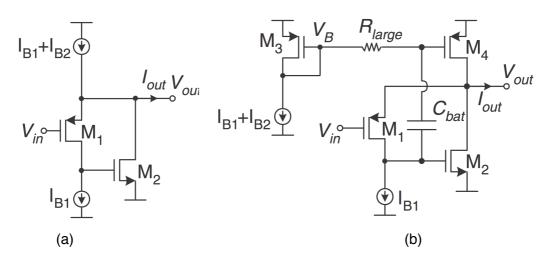

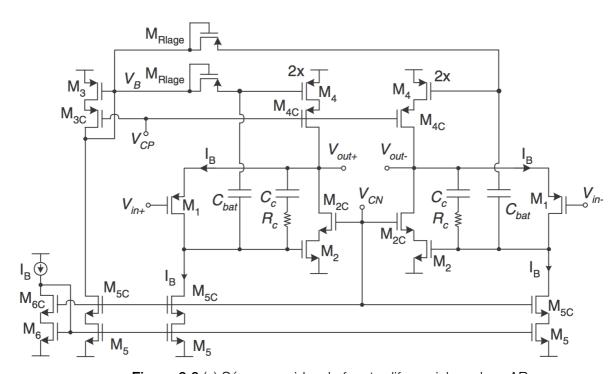

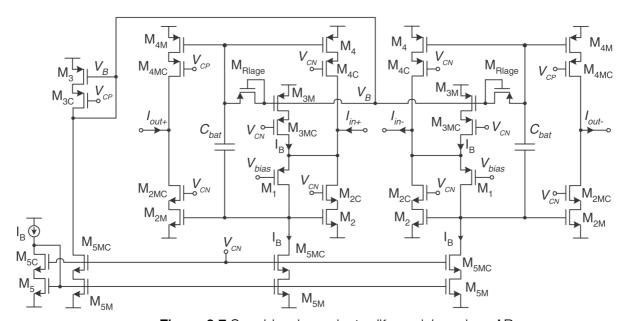

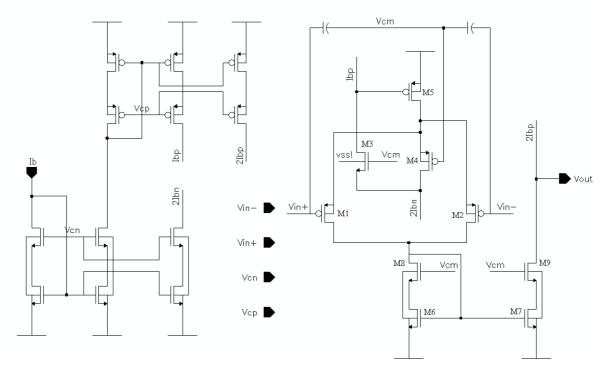

El seguidor de tensión que se va a utilizar en el esquema definitivo es una versión diferencial de el súper seguidor de fuente en clase AB introduciendo además la configuración cascodo en los espejos para obtener mejores copias de la corriente de polarización. El esquema es el mostrado en la figura 3.6:

Figura 3.6 (a) Súper seguidor de fuente diferencial en clase AB

Además de los transistores cascodo se ha introducido una compensación Miller para mejorar la estabilidad del sistema. El nodo de salida y el del drenador de  $M_1$  tienen sendos polos que pueden estar cercanos en frecuencia, lo que hace que la respuesta sea inestable. para evitarlo, se introduce  $C_c$  que aleja esos polos. Sin embargo ese condensador puede crear un cero que se aleja mediante  $R_c$  para que no afecte a la respuesta en frecuencia.

#### Seguidor de corriente

Como aplicación de el súper seguidor de fuente en clase AB se puede implementar también un seguidor de corriente con una resistencia de entrada muy pequeña. La forma en que podemos transformar el seguidor de tensión en un seguidor de corriente es copiando la corriente sensada a la entrada mediante una réplica de los transistores  $M_2$  y  $M_4$ . La tensión de entrada esta fijada por la corriente de polarización y la tensión externa  $V_{bias}$  de esta manera:

$$V_{in} = V_{bias} + V_{SG1} = V_{bias} + |V_{TH1}| + \sqrt{\frac{2I_{B1}}{\beta_1}}$$

(3.7)

En cuanto a parámetros del esquema, la resistencia de entrada sigue la siguiente formula:

$$R_{out} \approx \frac{1}{(g_{m1} + g_{mb1})(g_{m2} + \alpha g_{m4})r_{o1}}$$

(3.8)

Nuevamente se volverán a utilizar los espejos de corriente en configuración cascodo para mejorar la copia que se realiza de la corriente e incrementar la resistencia de salida. Se ha utilizado, al igual que en el caso del seguidor de tensión, la versión diferencial del esquema, que se detalla en la figura 3.7.

Figura 3.7 Seguidor de corriente diferencial en clase AB

#### Resistencias

Se trata del par de resistencias  $R_1$  y  $R_2$  que aparecen en la figura 3.3 con la diferencia de que hay que incluir un par en cada rama del circuito ya que ahora la configuración es diferencial.

Las resistencias deben ser lo suficientemente grandes como para que la corriente que genera la tensión de entrada no sea muy grande y no sature el amplificador perjudicando su linealidad y lo suficientemente pequeñas como para que el ancho de banda de la señal de salida sea lo más amplio posible. Además, como ya se ha explicado anteriormente, estas resistencias sirven para ajustar la ganancia del amplificador mediante el ratio de sus valores.

#### Amplificador completo

Una vez escogidos todos los elementos del amplificador, su esquema simplificado queda como se muestra en la figura 3.8:

Figura 3.8 Esquema simplificado del amplificador

Una de las ventajas de este esquema es que al no estar directamente interconectadas la rama positiva y la rama negativa, no va a dar problemas el modo común ya que éste es intrínsecamente cero, debido a que las resistencias  $R_2$  están conectadas a tierra. Esto reduce la complejidad del circuito ya que no es necesario introducir un bloque de rechazo al modo común.

| Parámetro                 | Valor       |

|---------------------------|-------------|

| Tecnología                | 0.5 μm CMOS |

| Vss                       | -1.3 V      |

| Vdd                       | 2 V         |

| Consumo en reposo         | 1.55 mW     |

| Corriente de polarización | 12 μΑ       |

Tabla 3.1 Parámetros del amplificador

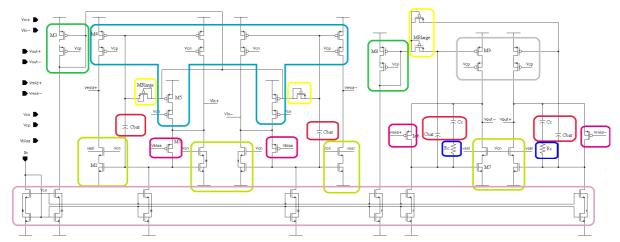

El esquema se presenta completo con los pines de entrada necesarios y con todas las corrientes de polarización fijadas por espejos en configuración cascodo en la figura 3.9. Las

resistencias de ajuste de ganancia se han colocado en la entrada y la salida del seguidor de corriente, que es el bloque de la izquierda del circuito. El bloque de la derecha corresponde al seguidor de tensión. Se han utilizado los valores de parámetros del circuito indicados en la tabla 3.1.

#### Dimensionamiento

Se ha utilizado para los transistores del circuito un dimensiones uniforme. Se hay separado los transistores en 4 grupos y se han dimensional todos los transistores de cada grupo de la misma manera. Los grupos son: Transistores P, Transistores N, transistores empleados en los espejos y transistores empleados como  $R_{large}$ . Este dimensionamiento se detalla en la siguiente tabla:

| Transistores       | W      | L       |  |  |  |

|--------------------|--------|---------|--|--|--|

| Р                  | 45 μm  | 600 nm  |  |  |  |

| N                  | 15 μm  | 600 nm  |  |  |  |

| Espejos            | 15 μm  | 1.05 μm |  |  |  |

| R <sub>large</sub> | 1.5 μm | 600 nm  |  |  |  |

**Tabla 3.2** Dimensionamiento de los transistores

Para dimensionar los transistores del circuito hay que tener en cuenta la influencia de la anchura y longitud de los transistores en el funcionamiento del mismo. El ratio W/L influye en la resistencia parásita del transistor. La anchura (W) influye en la cantidad de corriente que puede soportar, más corriente cuanto más ancha, sin embargo el consumo del transistor también aumenta. Por otro lado, la longitud (L) influye en la velocidad del transistor, cuanto más pequeña es la L mayor es la velocidad del transistor. La contrapartida es que en la configuración de espejo, la corriente se copia mejor si aumenta la longitud del transistor.

Para los transistores encargados de guiar la señal a lo largo del circuito, que son los N y los P se ha elegido una longitud de 600 nm porque es el mínimo permitido por la tecnología utilizada y esto hace los transistores más rápidos. La elección de la longitud mínima proporciona por tanto un ancho de banda mayor. En cuanto a la anchura se han dimensionado más grandes los transistores P que los N porque su transconductancia es aproximadamente 3 veces menor. Los tamaños de 15 y 45  $\mu$ m se han elegido por ser suficientemente grandes como para dar una linealidad alta al circuito y no lo bastante como para que el consumo se dispare.

Para los transistores de los espejos la anchura de  $15\,\mu$  m resultó suficiente para la corriente de polarización utilizada y se fijaron a  $1.05\,\mu$ m de longitud, que es un poco más que el mínimo permitido para que las copias de las corrientes fuesen más exactas.

Los transistores dedicados a  $R_{large}$  se han dimensionado al mínimo de sus dos dimensiones ya que dan la resistencia suficiente ocupando el mínimo de área posible.

Además de estos valores, los condensadores  $C_c$  y  $C_{bat}$  son de 0,5 pF y la resistencia  $R_c$  es de 50 k $\Omega$ . El esquema definitivo se presenta en la figura 3.9.

#### Simulaciones

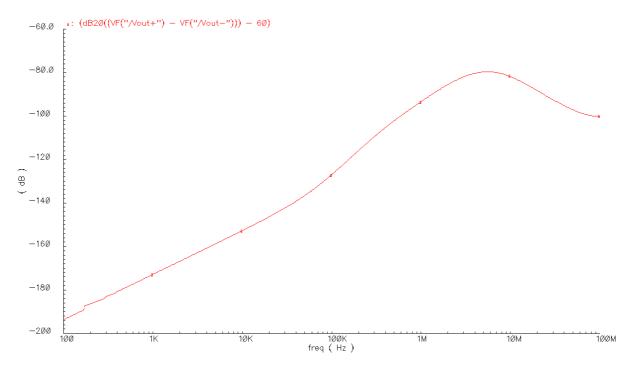

Las simulaciones realizadas han sido tres. Una medida del transitorio de la señal, una de la respuesta en frecuencia y por último la distorsión total armónica del circuito, que es muy importante para asegurarse de que la salida es fiel a la entrada, es decir, que el circuito es lineal.

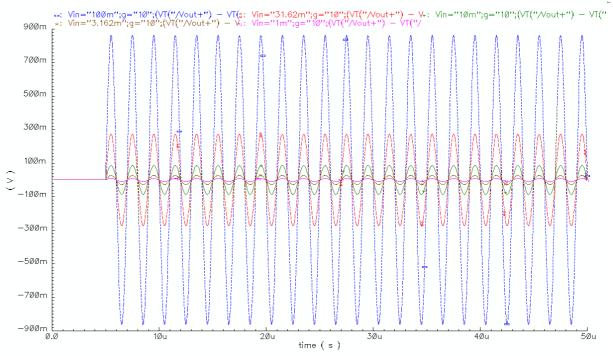

Para la medida del estado transitorio del circuito se ha introducido una señal que comienza después de  $5~\mu s$  y tal y como se ve en la gráfica 3.1 la respuesta del sistema es inmediata.

Gráfica 3.1 Respuesta transitoria G=1

El amplificador ha sido diseñado para trabajar configurado a una ganancia entre 1 y 10, es decir entre 0 dB y 20 dB de tensión. La finalidad de esto es conseguir un amplificador de 0dB a 60 dB colocando tres etapas en cascada. Para comprobar que el cambio de ganancia no afecta a la respuesta transitoria se presenta la gráfica 3.2, donde se representa la respuesta del sistema configurado a ganancia 10. Podemos comprobar que ese cambio de ganancia no afecta a la respuesta transitoria.

Con esta señal en el tiempo calculamos también la distorsión total armónica del sistema realizando dos análisis paramétricos variando la tensión de entrada. En uno de ellos se ha configurado la ganancia a 1 y en el otro a 10 tal y como se había hecho para calcular la respuesta transitoria. El resultado está representado en la gráfica 3.3.

Se puede considerar que el circuito tiene una linealidad adecuada ya que todos los valores de *THD* están por debajo de -40dB, sin embargo, cuanto menores sean estos valores mejor, más lineal será el circuito y por tanto es bueno buscar valores muy por debajo de esa cota.

**Gráfica 3.2** Respuesta transitoria G=10

Gráfica 3.3 Distorsión total armónica para G=1 y G=10

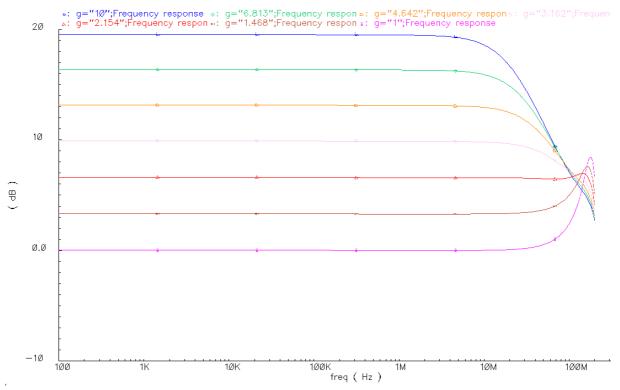

Una vez se ha comprobado que la respuesta del sistema es rápida y lineal, falta comprobar si va a ser válido para las frecuencias para las que se pretende utilizar, que están en torno a 1MHz. Para ello realizamos un análisis paramétrico en frecuencia variando la ganancia a la que esta configurado el amplificador.

Se debería obtener una respuesta que no varíe su ancho de banda en función de la ganancia ya que esta característica es inherente a la topología escogida para el diseño. En la gráfica 3.4 vemos que esto se cumple:

Además se comprueba que el ancho de banda es lo suficientemente grande como para trabajar a las frecuencias que se pretendía.

Gráfica 3.4 Respuesta en frecuencia del sistema

# Capítulo 4 Diseño del control de ganancia

Se han probado en el proyecto 3 técnicas de sintonía diferentes, de las cuales una es continua y dos discretas. El sistema de sintonía final se ha elegido discreto debido a los problemas que introducía la solución de sintonía continua. A continuación se van a detallar los diferentes procedimientos y las causas que han llevado a su elección o a su rechazo como parte final del circuito.

#### Descripción de Técnicas

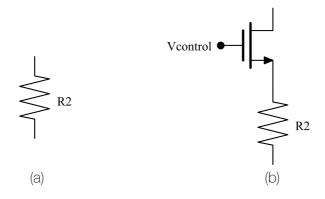

#### Control activo por medio de transistores

La sintonía continua proporciona un ajuste perfecto ya que puede configurarse la ganancia que se desee por medio de componentes activos controlados por una tensión.

La técnica de sintonía continua utilizada es la más sencilla hablando de técnicas de sintonía activa. y consiste en colocar transistores en triodo en serie con la resistencia  $R_2$ . La conexión de estos transistores se realizaría de la siguiente manera:

Figura 4.1 (a) Ganancia fija (b) Ganancia activa

Así, si variamos la tensión de control en un rango que no saque al transistor de su región de triodo, estaremos variando su resistencia interna y por lo tanto variando el valor de la ganancia dependiendo de esa tensión de control.

A pesar de variar el tamaño del transistor y demás parámetros, los resultados no fueron en ningún momento lo suficientemente buenos como para plantearse incluir esta implementación en el sistema, por lo tanto no se presentan esos datos. El principal perjudicado era el THD, ascendiendo incluso en algún caso a valores positivos.

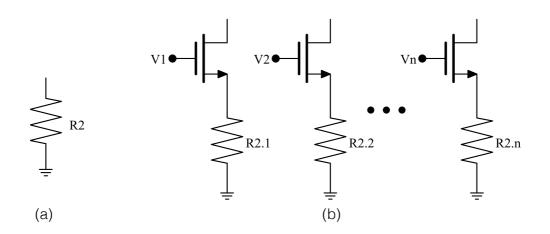

#### Array de resistencias pasivas

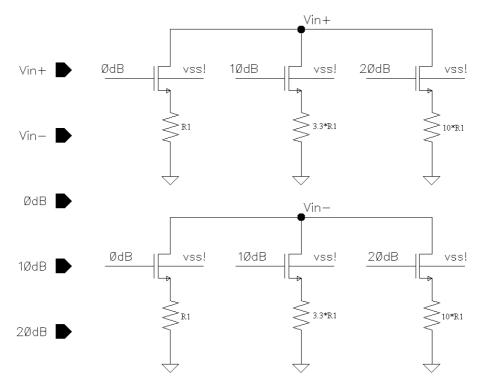

Una vez descartado el sistema de sintonía continua, el proyecto se centró en un sistema de sintonía discreta. Para esto se escogió la opción de colocar un array de resistencias en cada terminal intermedio colocando un transistor en serie con cada una de ellas. A diferencia del sistema anterior, esta vez lo que se busca es que el transistor opere en saturación o en corte dependiendo de si se quiere que la corriente circule por esa rama o no. El montaje es similar al anterior:

Figura 4.2 (a) Ganancia fija (b) Ganancia discreta

Lo que se busca pues es que cuando el transistor esta conduciendo, tenga la mínima influencia posible en la resistencia de la rama y que cuando esta en corte, su resistencia sea lo

suficientemente grande como para que toda la corriente circule por la rama que se encuentre activa en esos momentos. Esto segundo es fácil de conseguir y para conseguir lo primero basta con hacer el transistor un poco más grande que el tamaño mínimo.

Se ha pensado que el circuito tenga 7 escalones de ganancia, es decir, de 0 a 60 dB en saltos de 10 dB, por lo tanto cada etapa tiene que tener un array de tres resistencias. Para adecuarse a los escalones logarítmicos, las  $R_2$  correspondientes serán  $1*R_1$ ,  $3.3*R_1$  y  $10*R_1$ . De esta manera se pueden lograr todos los escalones ya que el esquema final va a constar de tres etapas.

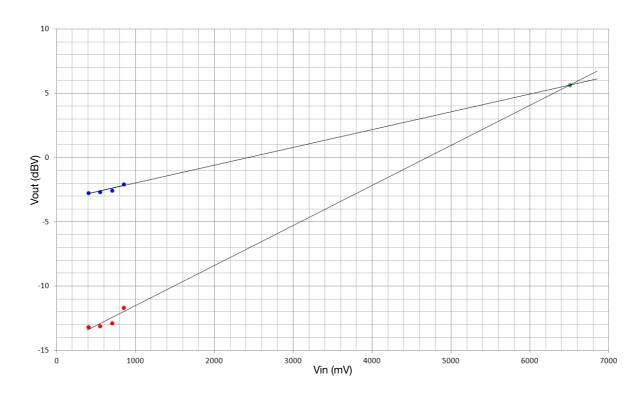

#### Control de ganancia

La idea del control de ganancia es medir el nivel de señal a la entrada para activar las ramas del array de resistencias pasivas según convenga, de modo que la señal de salida sea más o menos constante. De esta manera se va a conseguir que teniendo a la entrada señales de entre 1 mV y 1V, a la salida siempre se tengan señales de entre 300 mV y 1V.

Para ello, después de muchas pruebas e ideas se han seleccionado las dos alternativas que pueden ser válidas. Estas alternativas van a ser nombradas por el elemento que las diferencia, y que es además el cuello de botella del funcionamiento del sistema. La primera está basada en un elevador al cuadrado y la segunda en un detector de pico.

Los arrays, el codificador y el *ADC* aunque diferentes en implementación son iguales en esencia para las dos alternativas, por tanto su diseño va a diferir de una a otra en pequeños detalles derivados en su mayoría de las exigencias del primer bloque del control de ganancia.

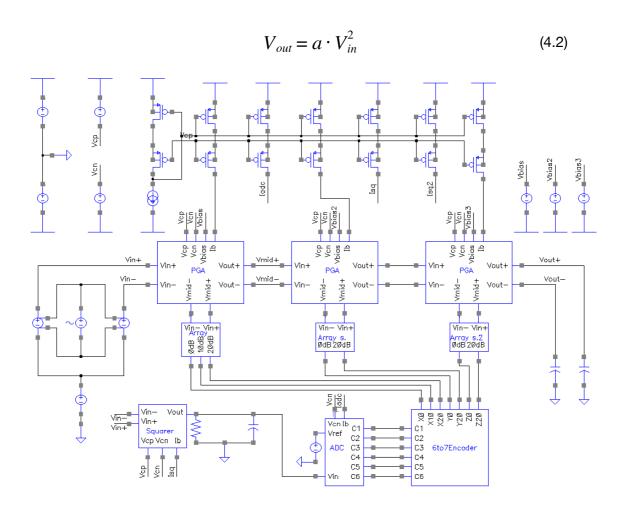

#### Alternativa del elevador al cuadrado

Esta alternativa consta, siguiendo el camino que realiza la señal de 3 principales bloques. El primero es un elevador al cuadrado con un filtro paso bajo en serie que extrae una tensión en *DC* proporcional al valor cuadrático medio de la señal. De ahí pasa a un *ADC* que distingue entre siete niveles que van a corresponder a los siete escalones en ganancia. Por último esas 6 señales pasan por el codificador que en función de ellas activan o desactivan las ramas de los arrays de resistencias.

Para configurar los escalones de ganancia basta con colocar 2 arrays de 2 posiciones, 0 dB y 20 dB y un tercero con 3 posiciones, 0 dB, 10 dB y 20 dB. En esta alternativa el array de 3 posiciones se va a colocar en la primera etapa. El esquemático resultante se detalla en la figura 4.3.

Se puede observar el bloque elevador, seguido de un paso bajo sencillo formado por una resistencia y un condensador. Uno de los problemas de este bloque es su tensión de salida, que es de la forma (4.1) y no (4.2):

$$V_{out} = V_o - a \cdot V_{in}^2 \tag{4.1}$$

Figura 4.3 Esquemático de la alternativa del elevador al cuadrado

La fórmula (4.1) lleva a pensar que colocando otro elevador con sus entradas cortocircuitadas como tensión de referencia para el ADC, la conversión se va a hacer sin problemas, sin embargo, ese nivel Vo de la tensión de salida depende además de la impedancia de entrada del pin al que se conecta. Este es otro de los problemas de esta implementación y se explicará más adelante cuando se hable del ADC.

El esquema del elevador al cuadrado se puede ver en la figura 4.4 y el dimensionamiento de sus transistores se muestra en la siguiente tabla:

| Transistor  | W       | L      |  |  |

|-------------|---------|--------|--|--|

| M1=M2=M3=M4 | 10.5 μm | 1.2 μm |  |  |

| M5          | 45 μm   | 1.2 μm |  |  |

| M6=M7=M8=M9 | 45 μm   | 900 nm |  |  |

Tabla 4.1 Dimensionamiento del elevador al cuadrado

Los transistores que aparecen en el esquema y sirven como alimentación del circuito se han dimensionado de la misma manera que los espejos de corriente utilizados para alimentar el amplificador del bloque básico.

Figura 4.4 Esquemático del elevador al cuadrado

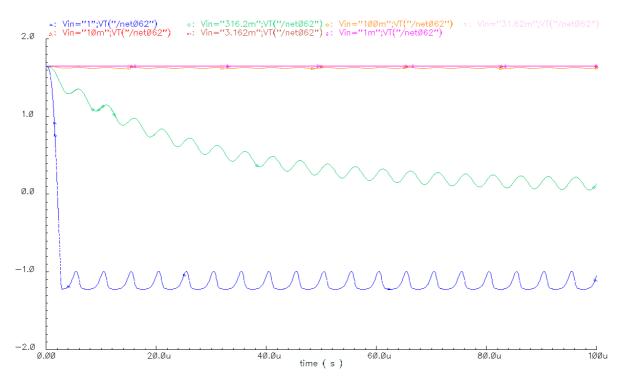

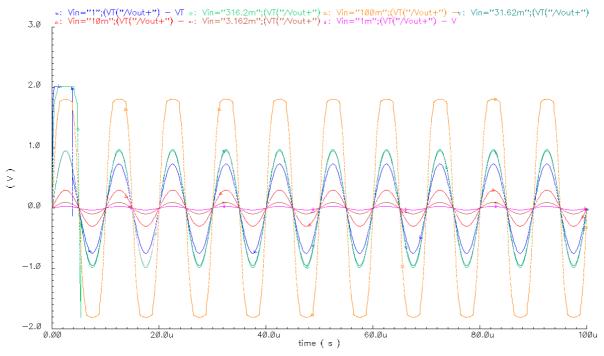

Para dar una muestra del comportamiento del elevador, se ha realizado un análisis paramétrico del nivel de la señal de entrada y el resultado es el que se muestra en la gráfica 4.1.

Gráfica 4.1 Señal de salida del elevador al cuadrado

Se puede observar que la señal se satura para la tensión más alta, pero eso no supone un problema ya que es para tensiones superiores a los 300 mV de entrada, que es el nivel que va a marcar la activación del primer escalón de ganancia.

El filtro paso bajo a la salida del elevador consta de un condensador de 30 pF y una resistencia de  $1 \text{M}\Omega$ .

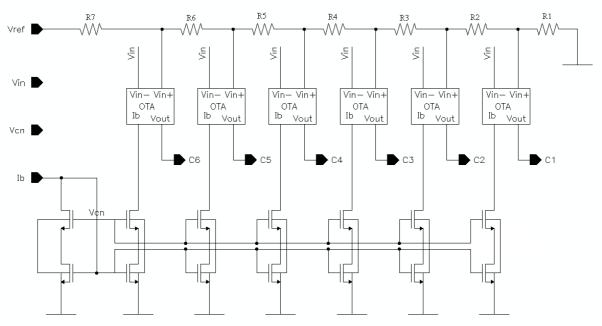

El siguiente bloque de esta alternativa es un *ADC*, es decir, un conversor analógico digital. La idea básica es comparar la señal por medio de un circuito sencillo con una serie de tensiones de referencia para distinguir los diferentes niveles. El funcionamiento de los comparadores se va a explicar más adelante. El esquemático del *ADC* es el de la figura 4.5.

Figura 4.5 Esquema del ADC de la alternativa del elevador

Como la salida del elevador al cuadrado es de la forma (4.1) va a dar tensiones más altas cuando la tensión a la entrada es de menor amplitud, por tanto  $C_6$  va a ser el comparador que decida si se fija la ganancia a 50 dB o a 60 dB, después,  $C_5$  lo hará entre 50 y 40 y así sucesivamente. Como los escalones son de 10 dB pero las tensiones están al cuadrado, la diferencia a la salida del elevador será de 20 dB por escalón. De esta manera haciendo un cálculo de las resistencias, una vez fijada  $R_1$ , para  $R_2$  hasta  $R_7$  seguirán la siguiente relación:

$$R_n = 10 \cdot R_{n+1} \tag{4.3}$$

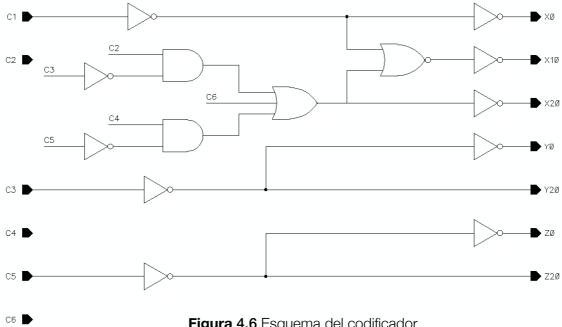

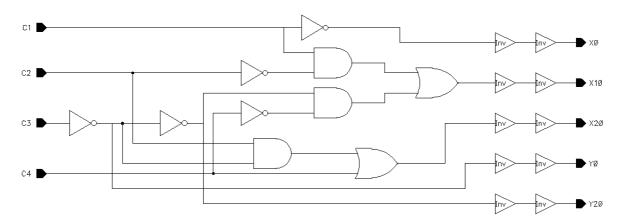

Tenemos pues seis señales digitales, pero estas no nos sirven para activar o desactivar las etapas convenientemente, de modo que hay que diseñar un codificador que tenga como entrada estas seis señales y de como salida las 7 señales requeridas, 3 para la primera etapa y 2 para cada una de las restantes.

Las combinaciones que se van a utilizar de los escalones de ganancia son 0 - 0 - 0, 10 - 0 - 0, 20 - 0 - 0, 10 - 20 - 0, 10 - 20 - 20 - 20 - 20 - 20 - 20. La razón de elegir estas combinaciones es que es más beneficioso en términos de inmunidad ante el ruido amplificar la

señal lo antes posible. El siguiente paso es realizar una tabla con las conversiones requeridas para calcular las funciones lógicas que se necesitan y poder realizar el diseño del circuito digital con las diferentes puertas lógicas. Todo esto se detalla en la tabla 4.2.

| Ganancia | C1 | C2 | СЗ | C4 | <b>C</b> 5 | C6 | Х0 | X10 | X20 | Y0 | Y20 | <b>Z</b> 0 | <b>Z20</b> |

|----------|----|----|----|----|------------|----|----|-----|-----|----|-----|------------|------------|

| 0        | 0  | 0  | 0  | 0  | 0          | 0  | 1  | 0   | 0   | 1  | 0   | 1          | 0          |

| 10       | 1  | 0  | 0  | 0  | 0          | 0  | 0  | 1   | 0   | 1  | 0   | 1          | 0          |

| 20       | 1  | 1  | 0  | 0  | 0          | 0  | 0  | 0   | 1   | 1  | 0   | 1          | 0          |

| 30       | 1  | 1  | 1  | 0  | 0          | 0  | 0  | 1   | 0   | 0  | 1   | 1          | 0          |

| 40       | 1  | 1  | 1  | 1  | 0          | 0  | 0  | 0   | 1   | 0  | 1   | 1          | 0          |

| 50       | 1  | 1  | 1  | 1  | 1          | 0  | 0  | 1   | 0   | 0  | 1   | 0          | 1          |

| 60       | 1  | 1  | 1  | 1  | 1          | 1  | 0  | 0   | 1   | 0  | 1   | 0          | 1          |

Tabla 4.2 Cálculo de funciones lógicas

Las cosas a tener en cuenta al diseñar esta tabla son no activar más de una rama de un mismo array ya que esto haría que el paralelo de las resistencias de ambas ramas diese como resultado una resistencia menor y por tanto una ganancia menor, y no tener nunca un array con rama activa. Esto último supondría una resistencia muy elevada y por tanto esa etapa estaría configurada a una ganancia que ni sería la deseada ni funcionaría de forma lineal.

Una vez fijadas las condiciones, las funciones resultante para cada señal de salida son:

$$X_0 = not (C_1)$$

$X_{10} = not (X_0 \text{ or } X_{20})$

$X_{20} = C_6 \text{ or } (C_4 \text{ and not } (C_5)) \text{ or } (C_2 \text{ and not } (C_3))$

$Y_0 = not (C_3)$

$Y_{20} = C_3$

$Z_0 = not (C_5)$

$Z_{20} = C_5$

$(4.4)$

Y de esta manera, el diseño de la circuitería es la detallada en la figura 4.6.

Se han añadido 2 inversores en los caminos de  $C_3$  y  $C_5$  para las salidas  $Y_0$  y  $Z_0$  porque no puede haber una entrada conectada directamente a una salida.

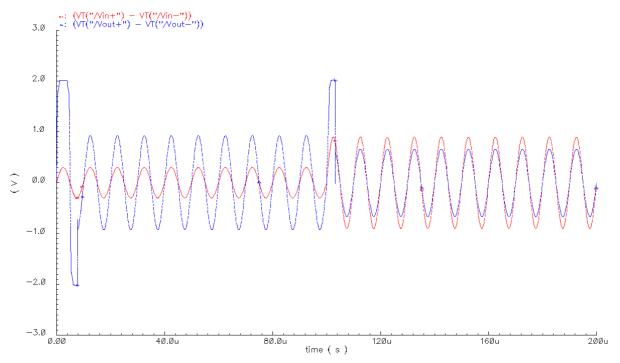

Acerca del funcionamiento final de esta alternativa se dan dos ejemplos donde se aprecia la dificultad del *ADC* para distinguir los niveles de tensión de entrada debido a que especialmente para las tensiones de entrada pequeñas las diferencias de tensión a la salida del elevador son mínimas. Por ello, las tensiones de salida del amplificador no se encuentran en el rango que deberían. Esto se aprecia bien en la gráfica 4.2:

Figura 4.6 Esquema del codificador

Gráfica 4.2 Tensión de salida de la alternativa del elevador

Se puede hacer aquí un comentario sobre el funcionamiento en clase AB y es que a pesar de estar alimentado entre -1.3 y 2 V, la tensión de salida (aunque saturada) va más allá de esos límites (ej. señal de color naranja).

En cuanto a la adaptación de la ganancia no es buena esta alternativa, sin embargo la respuesta transitoria es aceptable ya que los transitorios son de aproximadamente 10 µs. Para ilustrar esto se presenta la gráfica 4.3.

Gráfica 4.3 Transitorio de la alternativa del elevador

A pesar de tener ventajas, el funcionamiento general no es lo suficientemente bueno como para elegir esta alternativa para formar parte del diseño final, de modo que se deja aparte para poder ser desarrollada con más profundidad en un futuro. Con esto termina pues su análisis.

### Alternativa del detector de pico

Una vez descartada la alternativa del elevador pasamos a analizar la siguiente alternativa, que es la que esta basada en un detector de pico. El esquema va a ser similar a la alternativa anterior, un detector de pico, un *ADC*, un codificador y los arrays de resistencias. La principal diferencia es que la se toma como señal de entrada la señal que hay a la salida de la primera etapa. Esto se debe a que el rango de tensiones que tiene que distinguir el detector es menor, pero condiciona el diseño del circuito.

Dado que la entrada del detector es la salida de la primera etapa, hay que controlar esta mediante un lazo de retroalimentación. La forma que va a tener esta retroalimentación va a ser una señal llamada control, que se va a encargar de activar o desactivar la primera etapa. El primer efecto de esto es la nueva distribución de los arrays de resistencias. Ahora, el array con escalones de 10 dB se encuentra en la segunda etapa, dejando en la primera un array con solo dos posiciones que hace más sencilla la retroalimentación.

Siguiendo la misma estructura que se ha utilizado para explicar la alternativa anterior, el primer bloque es el detector de pico, cuya función es mantener a la salida una tensión en DC igual a la tensión de pico de la señal de entrada. La circuitería de transistores se encarga de rectificar la señal haciendo todo los semiciclos positivos y una vez se tiene esa forma, el condensador se encarga de mantener ese nivel de tensión cuando el semiciclo cae. Debido a que el condensador no es capaz de mantener ese nivel de forma ideal, la señal va a tener un

pequeño rizado. Ese rizado va a depender de dos factores, de la capacidad del condensador y de la corriente por la que se descargue. El rizado será menor cuanto mayor sea la capacidad del condensador, y será mayor cuanto mayor sea la corriente de descarga.

Esta disminución del rizado también tendrá un efecto negativo, ya que hará más lenta la respuesta del condensador a variaciones de la tensión de entrada, por lo tanto habrá que llegar a un compromiso a la hora de diseñar esta parte. El esquema del detector de pico es el de la figura 4.7.

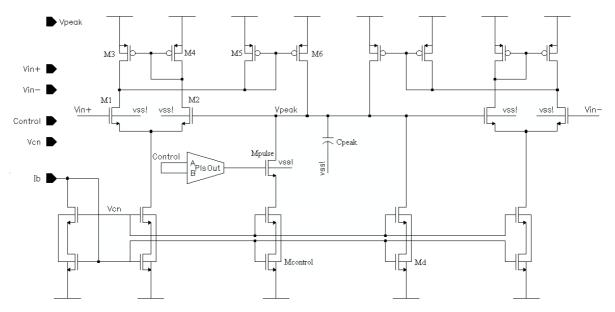

Figura 4.7 Esquema del detector de pico

Tras numerosas pruebas se han fijado los siguientes tamaños para los transistores del circuito, que son los que mejores resultados han ofrecido:

| Transistor | W      | L       |

|------------|--------|---------|

| M1=M2      | 30 μm  | 600 nm  |

| М3         | 150 μm | 600 nm  |

| M4         | 30 μm  | 600 nm  |

| M5=M6      | 18 μm  | 600 nm  |

| Md         | 1.5 μm | 1.05 μm |

| Mcontrol   | 45 μm  | 1.05 μm |

| Mpulse     | 1.5 μm | 600 nm  |

Tabla 4.3 Dimensionamiento del detector de pico

Al ser un circuito diferencial, se entiende que los transistores que son simétricos a los numerados del 1 al 6 tienen exactamente el mismo tamaño. Además, los transistores que

cumplen función de espejos no reflejados en la tabla tienen las mismas dimensiones que los espejos del bloque básico. Para terminar con los componentes queda decir que el valor del condensador es de 20 pF.

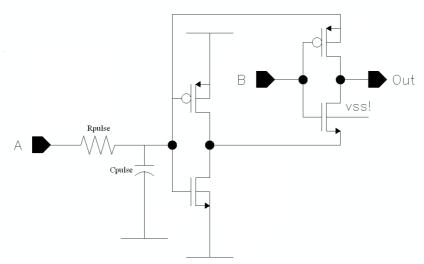

Aparece en la figura 4.7 un bloque llamado *Pls*. Se trata de un generador de pulsos. El hecho de que el condensador se descargue muy despacio da un problema cuando se desconecta (se cambia de 20 dB a 0 dB) la primera etapa, ya que la señal a la entrada del detector de pico cae bruscamente a un tercio de su valor. El transitorio de ese cambio es muy largo (en torno a 200 µs) debido a que la corriente de descarga es muy pequeña. Para ello se ha implementado este sistema, que descarga el condensador con una corriente mucho más grande cuando al señal de control varía. El sistema es sencillo y se trata simplemente de una puerta *XOR* cuya entrada *B* es la señal de control, y la entrada A la misma señal de control pero retrasada un tiempo determinado a través de un paso bajo *RC*. Su esquema es el de la figura 4.8.

Figura 4.8 Esquema del generador de pulsos

Al carecer la librería de cadence del modelo de la puerta XOR, ésta ha tenido que ser montada desde cero, además el esquema incluye ya la resistencia de 1  $M\Omega$  y el condensador de 2 pF. La corriente de descarga rápida y la anchura del pulso han sido calculados para que la tensión en el condensador caiga al valor adecuado y la transición sea lo más rápida posible.

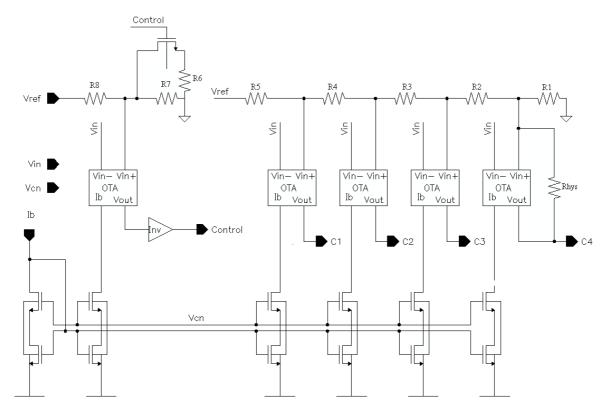

El siguiente bloque de esta alternativa es el *ADC*, que tiene dos partes principales, la dedicada a la señal de control, es decir, a ajustar la primera etapa y la que es similar al anterior *ADC* para ajustar los escalones de ganancia de las otras dos etapas. La segunda parte tiene la misma estructura que el *ADC* de la alternativa anterior solo que con 4 comparadores en vez de 6. Sin embargo, la primera es una comparación con histéresis.

Cuando la señal de entrada es lo suficientemente pequeña como para que la primera etapa este trabajando a 20 dB, la señal de control debería cambiar para cambiar. Este cambio ha de producirse cuando la señal a la salida de la primera etapa es superior a 1 V. En ese momento, la primera etapa pasa a trabajar a 0 dB, por que que la señal a la entrada del detector de pico cae hasta unos 100 mV, por lo que la señal de control debería volver a cambiar cuando esa tensión a la salida de la primera etapa es inferior a los 100 mV.

El funcionamiento de esta parte del circuito es lento, ya que la propia señal de control, que es la salida del comparador es la que se encarga de cambiar el estado de la histéresis. Esto se puede observar en el esquema del ADC presentado en la figura 4.9

La tensión que habrá en la entrada positiva del OTA destinado a la señal de control dependerá, como se ha explicado en el párrafo anterior, de la propia señal de control, de manera que cuando la tensión de control sea igual a  $V_{dd}$  tendremos la fórmula (4.5). Cuando la tensión de control sea igual a  $V_{ss}$  tendremos la fórmula (4.6)

$$V_{in+} = \frac{\frac{R_6 \cdot R_7}{R_6 + R_7}}{R_8 + \frac{R_6 \cdot R_7}{R_6 + R_7}} \cdot V_{ref}$$

(4.5)

$$V_{in+} = \frac{R_7}{R_8 + R_7} \cdot V_{ref} \tag{4.6}$$

Por ello debemos fijar las tensiones que se necesitan para los dos diferentes estados y así calcular los valores de estas 3 resistencias. Es un tipo de histéresis.

En cuanto a las resistencias correspondientes a los otros OTA's, ha de fijarse  $R_1$  y después ir calculando el resto mediante divisores resistivos sucesivos una vez establecidas las tensiones de referencia deseadas para cada uno de ellos, la fórmula sería la siguiente:

$$R_{n+1} = \left(\frac{V_{n+1}}{V_n} - 1\right) \sum_{k=0}^{n} R_k \tag{4.7}$$

Donde  $V_n$  es la tensión entre las resistencias  $R_n$  y  $R_{n+1}$ . Para simplificar el diseño y reducir el número de pines se ha fijado la tensión  $V_{ref}$  a la tensión de alimentación positiva. Los resultados de las resistencias se muestran en la tabla 4.4.

Además de estos valores, el transistor utilizado en la parte de la señal de control tiene las siguientes dimensiones: W = 1.65  $\mu$ m; L = 600 nm.

| Resistencia | Valor    |

|-------------|----------|

| R1          | 100 kΩ   |

| R2          | 1.1 kΩ   |

| R3          | 4.1 kΩ   |

| R4          | 13.33 kΩ |

| R5          | 104.2 kΩ |

| R6          | 1.3 kΩ   |

| R7          | 48 kΩ    |

| R8          | 19 kΩ    |

Tabla 4.4 Resistencias del ADC

Figura 4.9 Esquema del ADC

También merece una explicación la resistencia  $R_{hys}$ . Las limitaciones a la hora de implementar el detector de pico hacen que la señal a la salida de ese bloque tenga un pequeño rizado, como se ha comentado anteriormente. Esto hace que si la señal es pequeña y próxima al valor que marca el cambio de escalón de ganancia ese rizado pueda hacer oscilar la salida del comparador, de manera que la ganancia del conjunto del sistema será intermitente entre dos valores y distorsionará la señal. Con la histéresis conseguimos que el comparador no vascule a la misma tensión cuando esta esta subiendo o cuando está bajando, por lo que eliminamos ese efecto negativo del rizado. La solución es una versión simplificada de la histéresis que se realiza con la tensión de control ya que esta versión solo requiere una resistencia de realimentación positiva. Solo se ha colocado en el último comparador ya que este efecto es más importante cuando la señal de entrada es pequeña y tiene efectos negativos si se coloca en todos los comparadores. Uno de ellos es que hace el circuito más lento.

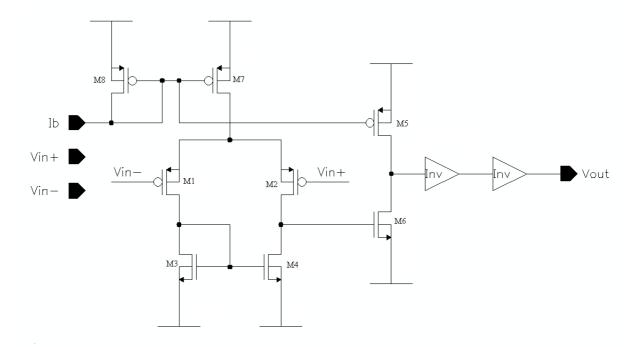

Antes de pasar a hablar del siguiente bloque falta por explicar el OTA Miller, que es el bloque utilizado como comparador. A pesar de ser un OTA, un tipo de amplificadores pensados para tener pendientes más suaves, este ha sido dimensionado para que una pequeña diferencia de tensión entre sus entradas lleve la salida a su estado de saturación, es decir, a la tensión de alimentación que corresponda.

Al diseño, se han añadido, para que la salida sea más cercana a las tensiones de alimentación, dos inversores que incrementan la sensibilidad del comparador para la tarea deseada ya que disparan la señal de salida. Estos dos inversores han sido implementados aparte ya que los inversores prediseñados en la librería de cadence están conectados a  $V_{dd}$  y a tierra, en vez de a  $V_{dd}$  y  $V_{ss}$  como requiere la aplicación. La figura 4.10 muestra el esquema de este bloque.

Figura 4.10 Esquema del OTA miller

El dimensionamiento de los transistores se detalla en la tabla 4.5.

| Transistor | Valor   |        |

|------------|---------|--------|

| M1=M2      | 45 μm   | 600 nm |

| M3=M4      | 30 μm   | 600 nm |

| M5=M8      | 37.5 μm | 600 nm |

| M6         | 97.5 μm | 600 nm |

| M7         | 24 μm   | 600 nm |

Tabla 4.5 Dimensionamiento del OTA Miller

Por último acerca del OTA queda comentar que el utilizado en el ADC para la señal de control es diferente al resto. Su diferencia es que los transistores  $M_5$  y  $M_6$  son más pequeños para hacer más rápido su funcionamiento. Solo cambia su W que es respectivamente 1.5 y 3  $\mu$ m. El efecto de este cambio se explicara en el capítulo 5 junto con la presentación de las gráficas.

El siguiente bloque del sistema es el codificador, que ajusta el funcionamiento de los arrays en función de las señales que le llegan del *ADC*. En esta ocasión son 4 las señales que salen del *ADC* para controlar los arrays y 5 las salidas del codificador, ya que el array de la primera etapa es controlado mediante la tensión de control. Las conversiones necesarias son las mostradas en la tabla 4.6.

Ahora, con de esta tabla extraemos las funciones lógicas que se necesita implementar para el diseño. Estas fórmulas son las que aparecen en (4.8)

| Ganancia |    | C1 | C2 | C3 | C4 | Y0 | Y10 | Y20 | <b>Z</b> 0 | <b>Z20</b> |

|----------|----|----|----|----|----|----|-----|-----|------------|------------|

|          | 0  | 0  | 0  | 0  | 0  | 1  | 0   | 0   | 1          | 0          |

| 1        | 10 | 1  | 0  | 0  | 0  | 0  | 1   | 0   | 1          | 0          |

| 2        | 20 | 1  | 1  | 0  | 0  | 0  | 0   | 1   | 1          | 0          |

| 3        | 30 | 1  | 1  | 1  | 0  | 0  | 1   | 0   | 0          | 1          |

| 4        | 10 | 1  | 1  | 1  | 1  | 0  | 0   | 1   | 0          | 1          |

Tabla 4.6 Cálculo de funciones lógicas

$$Y_{0} = not (C_{1})$$

$$Y_{10} = (C_{1} \ and \ not (C_{2})) \ or (C_{3} \ and \ not (C_{4}))$$

$$Y_{20} = C_{4} \ or (C_{2} \ and \ not (C_{3}))$$

$$Z_{0} = not (C_{3})$$

$$Z_{20} = C_{3}$$

$$(4.8)$$

Después, con estas fórmulas construimos el circuito necesario mediante puertas lógicas. El esquema del mismo es el siguiente:

Figura 4.11 Esquema del Codificador

Se han añadido dos inversores de los implementados manualmente a la salida para conseguir que la señal oscile entre  $V_{dd}$  y  $V_{\rm ss}$  tal y como se ha explicado en el apartado correspondiente al OTA.

La última parte del sistema de control de ganancia corresponde a los arrays de resistencias pasivas. Éstos no son más que un conjunto de resistencias en paralelo controladas individualmente por las señales que salen del codificador. Ese control se realiza mediante transistores actuando como interruptores. Los transistores elegidos son de tipo N y de una anchura de 15 µm y longitud mínima.

Figura 4.12 Esquema del array

Este tamaño se ha elegido para que el transistor tenga poca resistencia parásita cuando esta conduciendo y esto no afecte a la ganancia, ya que es una resistencia en serie que se suma a la propia del sistema. Además ha de ser lo suficientemente pequeño como para ser rápido y no limitar el ancho de banda del circuito.

Es importante también que haya en todo momento conduciendo un único transistor, ya que si hay más, la resistencia será el paralelo de ambas ramas y disminuirá, y con ella la ganancia. Y si no hay ninguno conduciendo la resistencia entre ese nodo y tierra será muy elevada, lo que aumentara la ganancia del circuito sacándola de su rango lineal de operación.

En la figura 4.12 se presenta el esquema del array utilizado en la segunda etapa. Los utilizados en las otras dos son similares, pero tienen únicamente 2 ramas.

Las resistencias corresponden a múltiplos de R<sub>1</sub> de tal manera que las ganancias de cada una son las expresadas en las etiquetas de las puertas de los transistores. Los otros dos arrays carecen de la rama de 10 dB.

Todos los resultados de simulación así como el esquema final del bloque completo serán presentados y comentados en el capítulo 5.

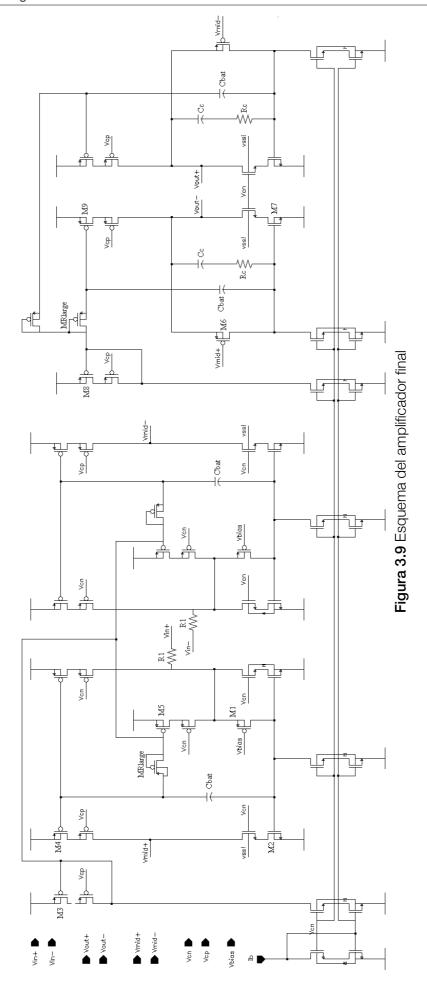

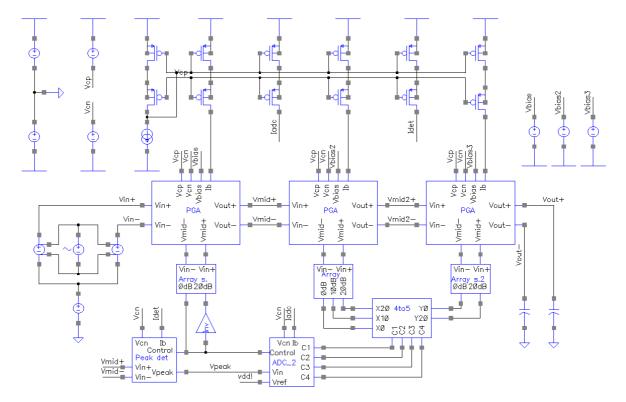

# Capítulo 5 Amplificador de ganancia programable

Tras haber explicado bloque por bloque el funcionamiento primero del amplificador en si y después del control de ganancia, hay que hablar del diseño final del bloque completo y también de su funcionamiento en las simulaciones. Hay que hacer dos comentarios antes de mostrar los resultados.

Primero, las tensiones  $V_{cn}$  y  $V_{cp}$  son las utilizadas para polarizar correctamente los transistores en cascodo. Estas dos tensiones son para los transistores NMOS y PMOS respectivamente. No se ha hablado anteriormente ni se les ha puesto etiquetas a estos transistores debido a que su función es únicamente mejorar la respuesta del sistema, se sustituye un único transistor por esta configuración de dos transistores. En todos los casos salvo una excepción, estos transistores tienen una W un 40% más grande y la misma L que los transistores a los que acompañan. Esta excepción es el cascodo correspondiente a  $M_{\rm d}$ , que es la parte del espejo de corrientes del detector de pico por la que se descarga el condensador. En ese caso, ambos transistores son del mismo tamaño porque lo primordial en ese caso era que la corriente de descarga fuese pequeña.

Segundo, las tensiones de polarización ( $V_{bias}$ ,  $V_{bias2}$  y  $V_{bias3}$ ) han sido específicamente calculadas para que cada etapa y además el circuito es bastante sensible a variaciones en las mismas. Por ello en caso de crear un layout y fabricar este sistema, habría que incluirlas como

pines de entrada y ajustar sus valores cuidadosamente para que el circuito funcionase correctamente.

Figura 5.1 Esquema completo del amplificador

Se han colocado además como carga unos condensadores de 300 fF que es la capacidad típica de la puerta de un transistor MOS y por lo tanto es una medida realista de la carga cuando se introduce el control automático de ganancia.

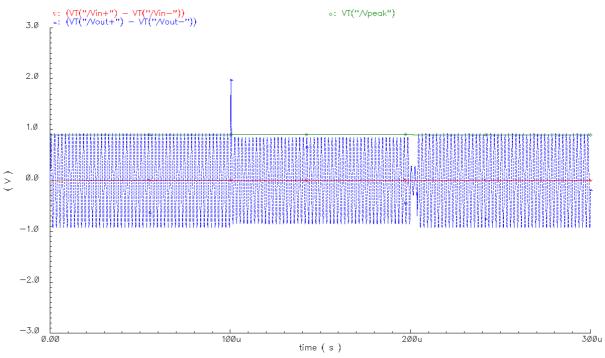

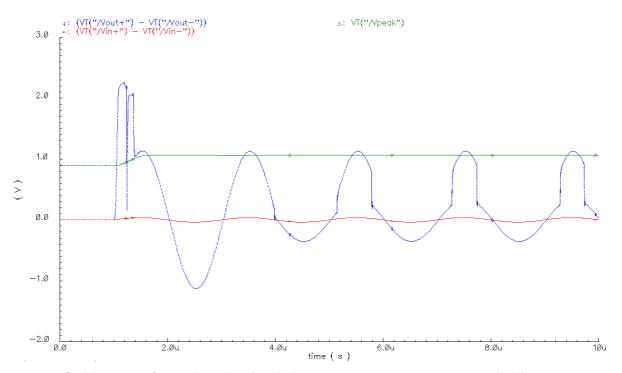

## Respuesta transitoria

La primera medida a realizar es la respuesta transitoria, y no solo la inicial cuando el circuito esta en reposo y empieza a funcionar, sino que al haber escalones de ganancia, se producen respuestas transitorias cada vez que la señal de entrada crece o decrece forzando al circuito a saltar a otro escalón.

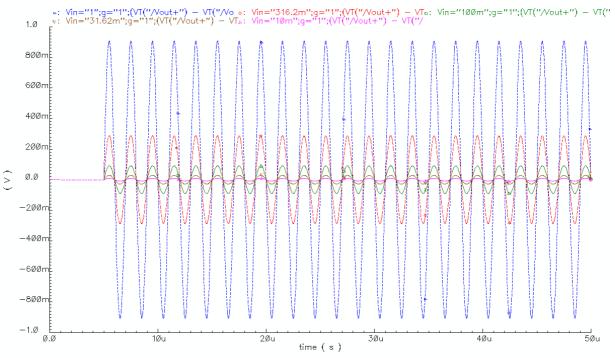

Así, hay 12 transitorios posibles, dos por cada salto de escalón de ganancia, uno ascendiendo y otro descendiendo. Se van a presentar los resultados en 6 gráficas diferentes. En cada una se ve el salto a un escalón inferior (la señal de entrada crece) y la posterior vuelta a un escalón de ganancia superior (la señal de entrada decrece). En la presentación de los resultados no se incluye una gráfica específica para mostrar comportamiento al empezar a funcionar porque en todas las correspondientes a los cambios de ganancia se puede ver que el transitorio inicial es inexistente.

Las gráficas presentan los primeros 300 µs de operación, donde los 100 primeros corresponden a un nivel de señal, durante los 100 posteriores el nivel de señal se triplica y en

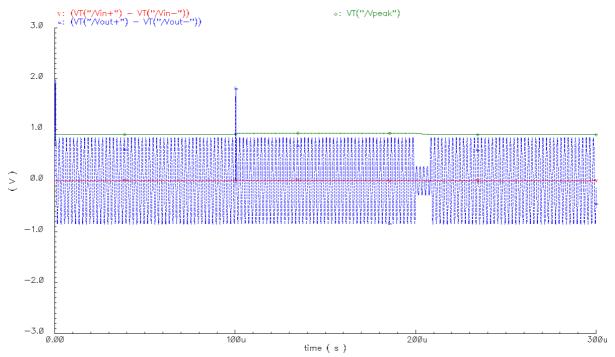

los 100 últimos la señal vuelve a ser la del principio. La primera, la gráfica 5.1, muestra señales de 1 mV y 3 mV que corresponden a 60 dB y 50 dB de ganancia respectivamente.

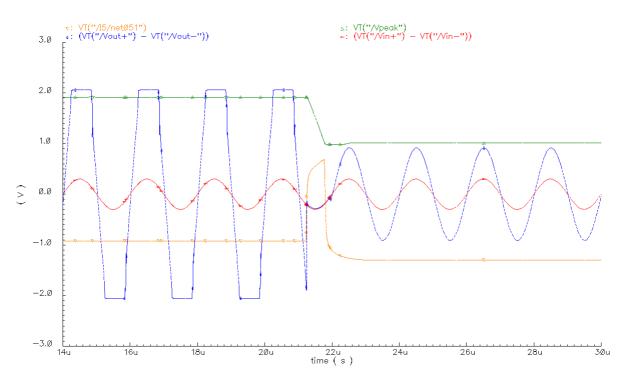

**Gráfica 5.1** Señal de entrada variando entre 1 mV y 3 mV (rojo), señal de salida (azul) y salida del detector de pico (verde)

Las transiciones son rápidas, tanto al principio, ya que el amplificador empieza a funcionar instantáneamente al detectar señal de entrada, como en los dos escalones. El pico que aparece en la señal para t = 100 µs es debido a que la señal de entrada crece y el amplificador todavía no lo ha detectado, pero su estrechez demuestra la rapidez del sistema para adaptarse a los cambios. Después, intervalo de tiempo alrededor de t = 200 µs en el que la señal cae y el amplificador no cambia la ganancia se debe a que el condensador utilizado para el detector de pico tarda en descargarse.

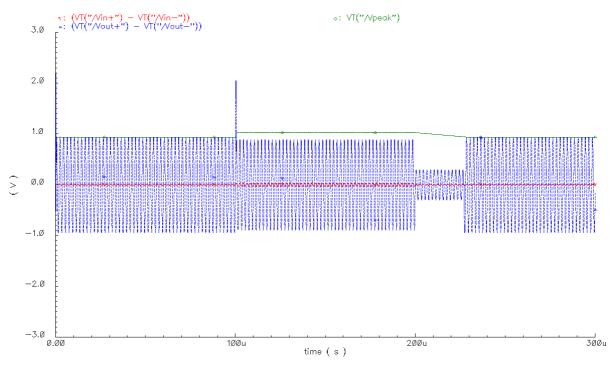

La siguiente gráfica, la 5.2, muestra la señal de entrada variando entre 3 mV y 9 mV, es decir, entre 50 dB y 40 dB de ganancia.

Antes de aplicar la señal, la entrada en el detector de pico es de 0 V, por lo tanto, el amplificador, por defecto, siempre arranca configurado a 60 dB, Podemos comprobar esto en la gráfica 5.2 ya que tenemos un pico de tensión en la tensión de salida (señal azul) en t = 0 s que antes no aparecía. Nuevamente, el pico es de muy corta duración ya que el amplificador se adapta rápidamente a los 50 dB que corresponden a la señal de 3 mV. Como se ha comentado en la gráfica 5.1, la adaptación a un escalón de ganancia superior (de 40 dB a 50 dB en este caso) se ralentiza debido a que el condensador ha de ser de un tamaño considerable para que el rizado sea pequeño, pero esto lo hace más lento a cambios de nivel de entrada. Sin embargo, ese intervalo es algo irreal ya que se debe al salto brusco de la amplitud. En una situación real, la señal variará más lentamente y ese efecto no será apreciable.

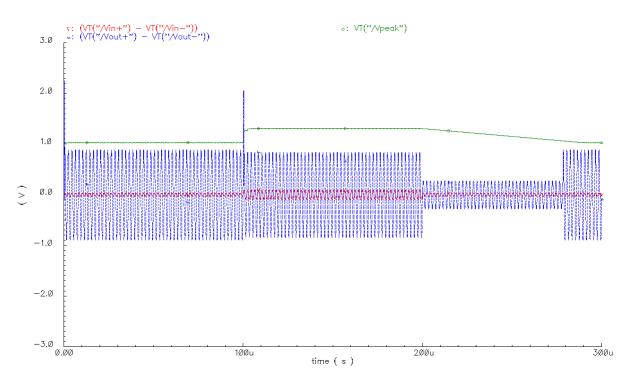

El siguiente escalón de ganancia es el de 30 dB - 40 dB - 30 dB y es el presentado en la gráfica 5.3 mediante señales de entrada que varían entre 10 mV y 30 mV.

**Gráfica 5.2** Señal de entrada variando entre 3 mV y 9 mV (rojo), señal de salida (azul) y salida del detector de pico (verde)

Tal y como ocurría en la gráfica 5.2, tenemos los picos de tensión en t=0 s y en t=100 µs por las mismas causas que en la situación anterior. La tensión de salida del detector de pico (señal verde en las gráficas) sufre ya una variación más grande al ser 20 mV el escalón entre las dos señales, esto hace también que el condensador tarde más en descargarse hasta el nuevo

**Gráfica 5.3** Señal de entrada variando entre 10 mV y 30 mV (rojo), señal de salida (azul) y salida del detector de pico (verde)

nivel cuando la señal de entrada decrece y por lo tanto, el transitorio que comienza en 200 µs es más largo. Esto último tiene la misma explicación que en el caso anterior y su efecto en el funcionamiento real del sistema seria menor.

La gráfica 5.4 presenta los escalones de ganancia entre 20 dB y 30 dB mediante señales que varían entre 30 mV y 90 mV.

**Gráfica 5.4** Señal de entrada variando entre 30 mV y 90 mV (rojo), señal de salida (azul) y salida del detector de pico (verde)

El comentario acerca de la gráfica 5.3 explica perfectamente lo que ocurre en esta gráfica 5.4. Lo que cambia es que el transitorio que comienza en  $t=200~\mu s$  es todavía más largo ya que esta vez el salto es de 60~mV, pero al igual que antes, es causa de la situación artificial del análisis.

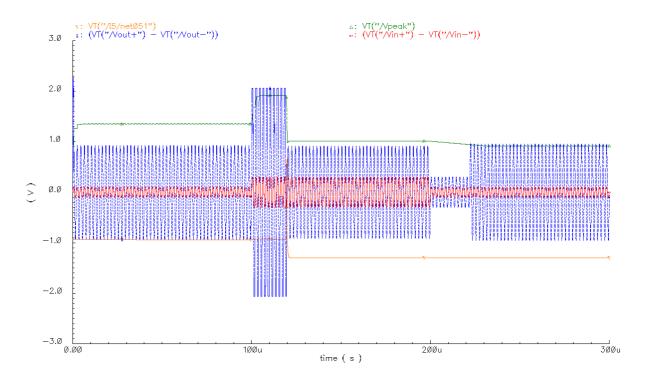

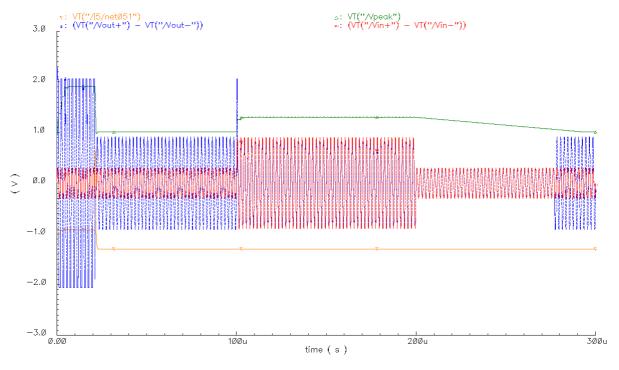

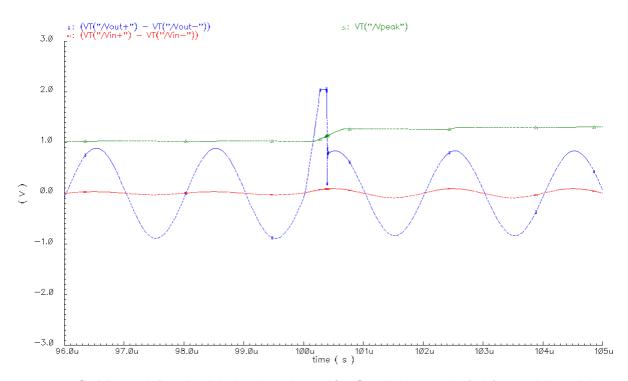

La situación es distinta ya en la gráfica 5.5. Se trata de los cambios de ganancia entre 10 dB y 20 dB, lo que conlleva actuar sobre la primera etapa que esta controlada mediante una realimentación y por tanto su respuesta va a ser más lenta. Algunos efectos que aparecían anteriormente siguen estando presentes, como el pico de tensión en t = 0 s ya que el amplificador sigue estando configurado a 60 dB al empezar a funcionar debido al diseño.

Paso por paso, el comportamiento hasta  $t=100\,\mu\,s$  es el mismo que en gráficas anteriores, y el primer cambio que nos encontramos es en el transitorio debido al aumento de nivel de señal de entrada, es decir, cuando la ganancia pasa de 20 dB a 10 dB. En esa situación, la primera etapa pasa de 20 dB a 0 dB y la segunda de 0 dB a 10 dB. La encargada de cambiar la primera etapa es la señal de control, sin embargo, en la primera parte del *ADC* (figura 4.9) vemos como la señal de control esta controlada por ella misma, de modo que su respuesta ante los cambios es más lenta, lo que provoca que pasen aproximadamente 20  $\mu$ s

**Gráfica 5.5** Señal de entrada variando entre 100 mV y 300 mV (rojo), señal de salida (azul), salida del detector de pico (verde) y pulso de descarga (naranja)

desde que la señal de entrada cambia hasta que el amplificador ajusta la ganancia al nuevo nivel.

La caída que sufre la tensión de entrada del detector al desconectarse la primera etapa es muy brusca y además, a diferencia de los anteriores saltos, que son debidos a la situación artificial del análisis, este salto se produciría en un escenario real de la misma manera, por lo que hay que evitarlo. Para ello esta el generador de pulsos, que descarga el condensador rápidamente tal y como se ha explicado en el capítulo anterior. La gráfica 5.6 detalla ese comportamiento.

Por último, el escalón creciente que sucede a los 200 µs sufre un retraso como el de los anteriores casos y debido a las mismas causas. Se ha reducido el valor del condensador en esta medida para reducir ese transitorio y poder representar todos los escalones en la misma escala.

Queda entonces únicamente el último escalón por comentar, que es el que corresponde a ganancias de 0 dB y 10 dB y que se presenta en la figura 5.7 mediante señales de 300 mV y 900 mV.

La situación inicial es debido a la lentitud de adaptación de la señal de control, tal y como ocurría en el apartado anterior transcurridos 100 µs. En esta gráfica, para ese tiempo tenemos un pico de adaptación a la nueva tensión y después el retardo ya comentado cuando ésta decrece.

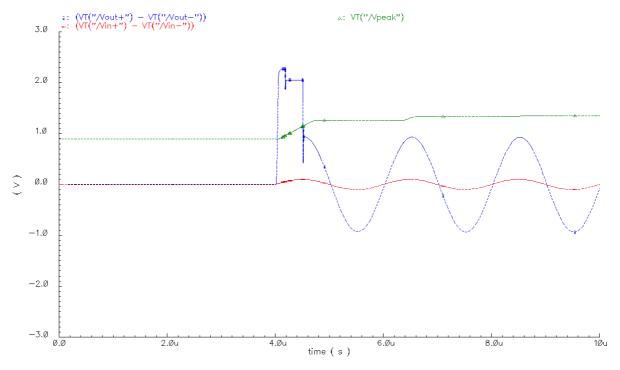

Para completar el análisis de los transitorios se añaden dos gráficas que muestran los dos picos de tensión comentados hasta ahora. El primero es debido a que la señal crece y antes de detectarlo, el amplificador sigue configurado a la misma ganancia por lo que la señal de salida

Gráfica 5.6 Detalle de la descarga rápida. Señal de entrada (rojo), señal de salida (azul), salida del detector de pico (verde) y pulso de descarga (naranja)

Gráfica 5.7 Señal de entrada variando entre 300 mV y 900 mV (rojo), señal de salida (azul), salida del detector de pico (verde) y pulso de descarga (naranja)

se dispara hasta que el sistema se adapta a la nueva situación, que como vemos en la gráfica 5.8 es alrededor de 500 ns.

**Gráfica 5.8** Detalle del pico de adaptación. Señal de entrada (rojo), señal de salida (azul) y salida del detector de pico (verde)

El segundo es el pico inicial, ya que al no haber entrada, el amplificador esta por diseño forzado a trabajar a 60 dB cuando empieza a haber señal, y una vez más, la salida se dispara hasta que el sistema se adapta a la señal de entrada. El retardo en este caso es también de 500 ns aproximadamente tal y como vemos en la gráfica 5.9.

**Gráfica 5.9** Detalle del pico inicial. Señal de entrada (rojo), señal de salida (azul) y salida del detector de pico (verde)

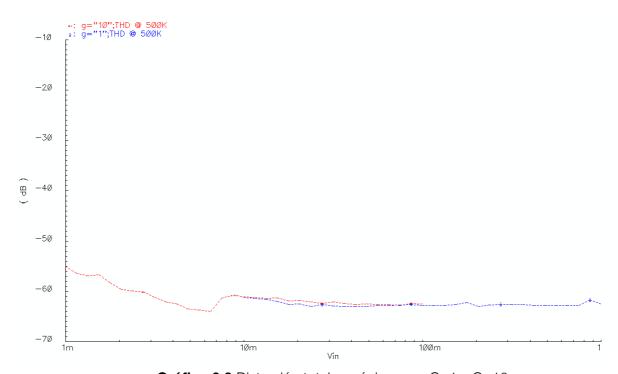

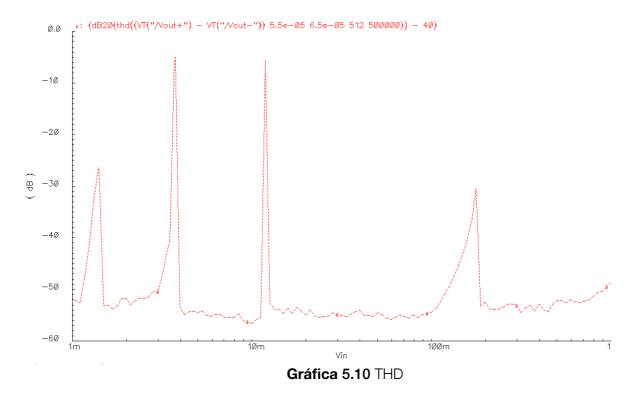

#### **THD**

La distorsión total armónica o *THD* de sus siglas en ingles es una medida de la linealidad del circuito. El objetivo es que el circuito sea lo más lineal posible, por lo tanto lo deseado es tener un nivel de *THD* bajo. El *THD* se calcula como dice la fórmula (5.1). Típicamente, es aceptable para esta aplicación un nivel por debajo de los -40 dB, pero cuanto más bajo sea mejor.

$$THD = \frac{\sum_{i=1}^{n} Potencia\ de\ armónico}{Potencia\ del\ tono\ fundamental}$$

(5.1)

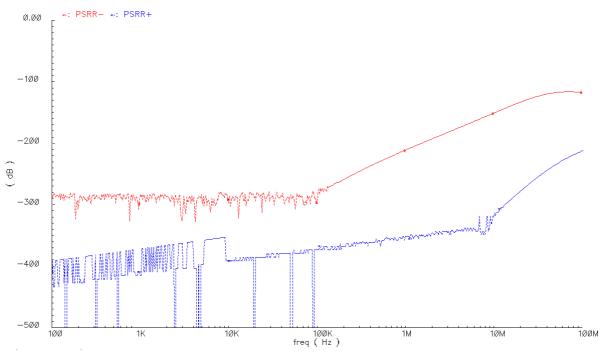

Realizando un análisis paramétrico de la señal de entrada se dibuja una gráfica con todos los niveles de *THD* de la señal de salida y el resultado es la gráfica 5.10